# DIRECT SUPPORT AND GENERAL SUPPORT MAINTENANCE MANUAL FOR

SATELLITE COMMUNICATION TERMINAL AN/TSC-54 (DETAILED CIRCUIT ANALYSIS) (NSN 5895-00-937-4993)

This copy is a reprint which includes current pages from Changes 1 and 2

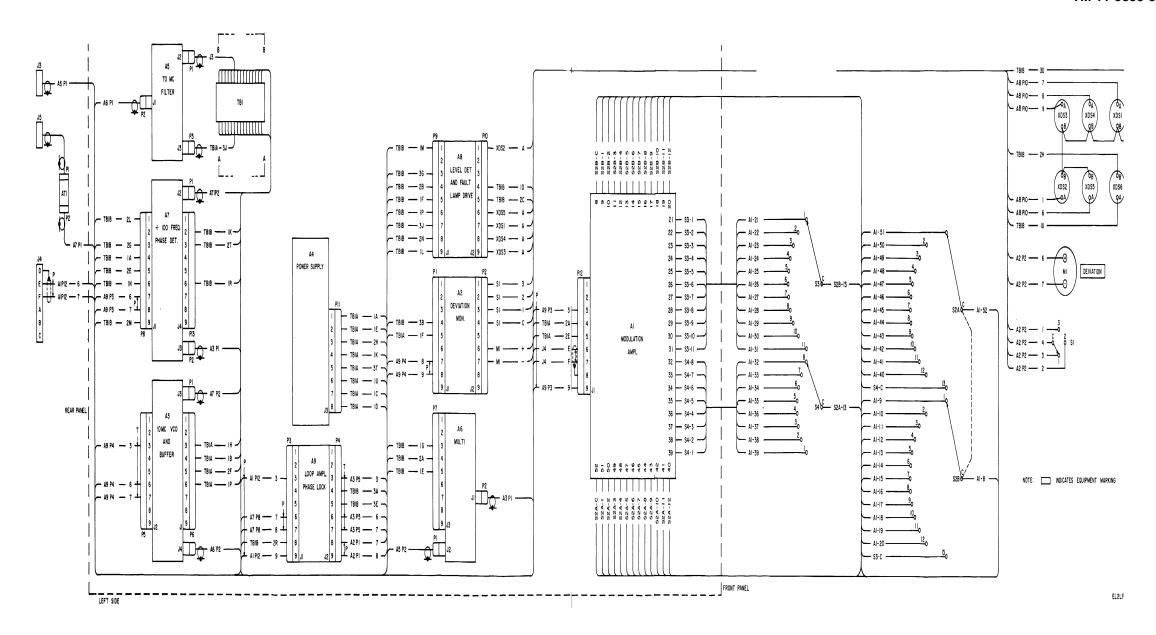

DEPARTMENTS OF THE ARMY, THE NAVY, AND THE AIR FORCE

JANUARY 1978

CHANGE No. 2

DEPARTMENTS OF THE ARMY, THE NAVY, AND THE AIR FORCE WASHINGTON, DC, 17 March 1980

# Direct Support and General Support Maintenance Manual SATELLITE COMMUNICATION TERMINAL AN/TSC-54 (DETAILED CIRCUIT ANALYSIS) (NSN 5895-00-937-4993)

TM 11-5895-389-34-2/NAVELEX 0967-LP-377-7090/TO 31R5-2TSC54-22-2, 5 January 1978, is changed as follows:

- 1. Remove old pages and insert new pages as indicated below.

- 2. New or changed material is indicated by a pointing hand, a shaded area, or a vertical bar in the margin of the page.

3. File this change sheet in the front of the publication for reference purposes.

By Order of the Secretaries of the Army, the Navy, and the Air Force:

E. C. MEYER

General, United States Army

Chief of Staff

Official:

J. C. PENNINGTON

Major General, United States Army

The Adjutant General

EARL B. FOWLER

Rear Admiral, United States Navy

Commander, Naval Electronic

Systems Command

Official:

LEW ALLEN, JR., General USAF Chief of Staff

BRYCE POE II General, USAF, Commander, Air Force Logistics Command

Distribution:

To be distributed in accordance with DA Form 12-51 Direct and General Support maintenance requirements for AN/TSC-54.

CHANGE No. 1

DEPARTMENTS OF THE ARMY, THE NAVY, AND THE AIR FORCE WASHINGTON, DC, 29 June 1979

# Direct Support and General Support Maintenance Manual SATELLITE COMMUNICATION TERMINAL AN/TSC-54 (DETAILED CIRCUIT ANALYSIS) (NSN 5895-00-937-4993)

TM 11-5895-389-34-2/NAVELEX 0967-LP-377-7021/TO 31R5-2TSC54-22-2, 5 January 1978 is changed as follows:

- 1. A vertical bar appears opposite changed material.

- 2. Remove and insert pages as indicated in the page list below:

| Remove                          | Insert                |

|---------------------------------|-----------------------|

| i through v                     | i through v           |

| 3-21 and 3-22                   | 3-21 through 3-22.3   |

| 3-119 through 3-124             | 3-119 through 3-124.1 |

| Figure FO 3-10                  |                       |

| None                            |                       |

| Figure FO 3-11 (sheets 1 and 2) |                       |

| Figure FO 3-54                  | Figure FO 3-54        |

3. File this change sheet in the front of the manual for reference purposes.

By Order of the Secretaries of the Army, the Navy, and the Air Force:

BERNARD W. ROGERS General, United States Army Chief of Staff

Official:

J. C. PENNINGTON Major General, United States Army The Adjutant General

EARL B. FOWLER Rear Admiral, United States Navy Commander, Naval Electronics Systems Command

> LEW ALLEN, JR., General USAF Chief of Staff

Official:

BRYCE POE II General, USAF, Commander, Air Force Logistics Command

#### **DISTRIBUTION:**

To be distributed in accordance with DA Form 12-51, Direct and General Support Maintenance requirements for AN/TSC-54 Equipment.

TECHNICAL MANUAL No. 11-5895-389-34-2

**NAVELEX**

No. 0967-LP-377-7020 TECHNICAL ORDER No. TO 31R5-2TSC54-22-2

DEPARTMENTS OF THE ARMY,

THE NAVY AND THE AIR FORCE

WASHINGTON, DC, 5 January 1978

# DIRECT SUPPORT AND GENERAL SUPPORT MAINTENANCE MANUAL FOR SATELLITE COMMUNICATION TERMINAL AN/TSC-54

(DETAILED CIRCUIT ANALYSIS) (NSN 5895-00-937-4993)

#### REPORTING OF ERRORS

You can improve this manual by recommending improvements using DA Form 2028-2 located in the back of the manual. Simply tear out the self-addressed form, fill it out as shown on the sample, fold it where shown, and drop it in the mail.

If there are no blank DA Forms 2028-2 in the back of your manual, use the standard DA Form 2028 (Recommended Changes to Publications and Blank Forms) and forward to the Commander, US Army Communications and Electronics Materiel Readiness Command, ATTN: DRSELME-MQ, Fort Monmouth, NJ 07703.

For Air Force, submit AFTO Form 22 (Technical Order System Publication Improvement Report and Reply) in accordance with paragraph 6-5, section VI, T.O. 00-5-1. Forward direct to prime ALC/MST.

For Navy, mail comments to the Commander, Navel Electronics Systems Command, Training and Publications Management Office, ELEX 04F3, P.O. Box 80337, San Diego, CA 92138.

In any case, a reply will be furnished direct to you.

# Each volume in this series contains a separate table of contents. The Index, however, is located in TM 11-5895-389-34-3, 5 January 1978. Paragraph Page

|            |                                      | raiayiapii | raye  |

|------------|--------------------------------------|------------|-------|

| CHAPTER 3. | DETAILED CIRCUIT ANALYSIS            | • .        | _     |

| Section I. | Components of operations control van | 3-1        | 3-1   |

| II.        | Antenna group components             | 3-34       | 3-121 |

# LIST OF ILLUSTRATIONS

| rigure | riue                                                                  | Page |

|--------|-----------------------------------------------------------------------|------|

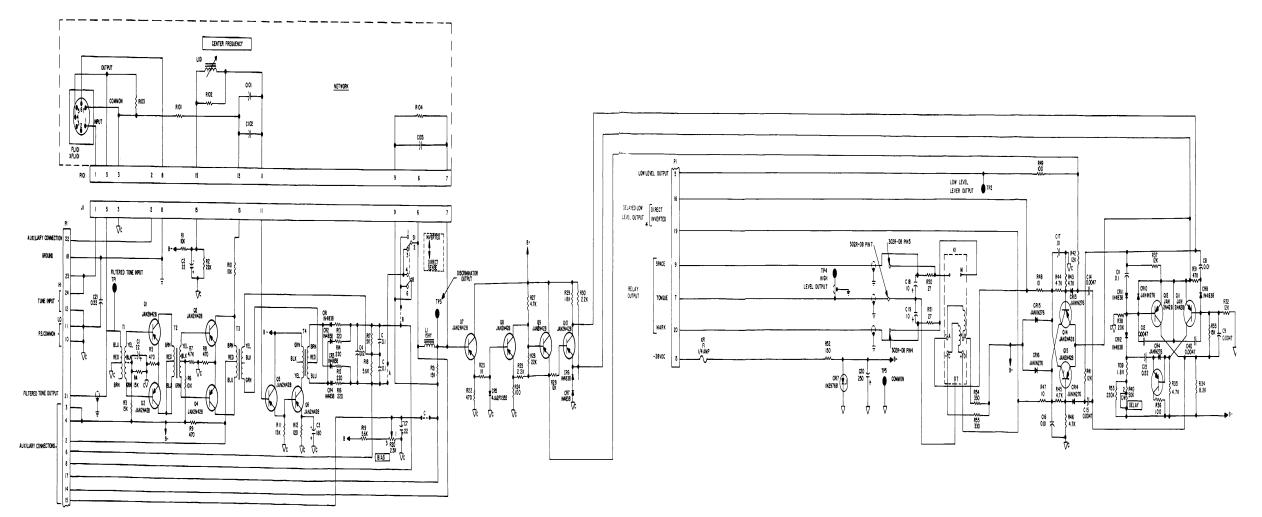

| 3-1    | Zero set control 1A2A1, schematic diagram                             | 3-3  |

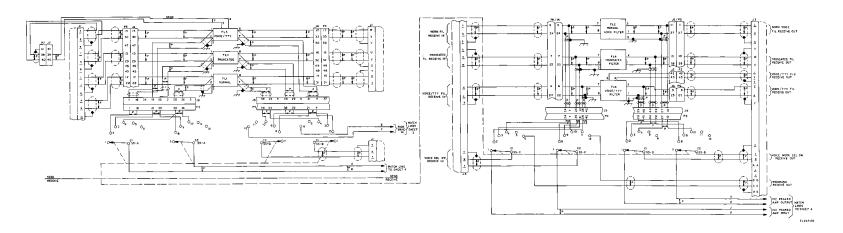

| 3-2①   | Frequency distribution unit 1A2A22, connection diagram (sheet 1 of 2) | 3-4  |

| 3-2    | Frequency distribution unit 1A2A22, connection diagram (sheet 2 of 2) | 3-5  |

| 3-3    | 1 MHz amplifier/limiter 1A2A22AR1, schematic diagram                  |      |

| 3-4    | 5 MHz amplifier/limiter 1A2A22AR2, schematic diagram                  |      |

| 3-5    | Preamplifier 1A2A33A5, schematic diagram                              |      |

| 3-6    | Output amplifier IA2A33A8, schematic diagram                          |      |

| 3-7    | Power section 1A2A33A1 and 1A2A33A2, schematic diagram                |      |

| 3-8    | + 28 vdc power supply PSI, input/output signal characteristics        | 3-11 |

| 3-9    | Typical +28 vdc/+10 vdc power supply, schematic diagram               | 3-12 |

| 3-10   | Servo amplifier AR1, input/output signal characteristics              |      |

| 3-11   | Relay driver, schematic diagram                                       | 3-14 |

| 3-12   | Servo operational amplifier A3, schematic diagram                     | 3-14 |

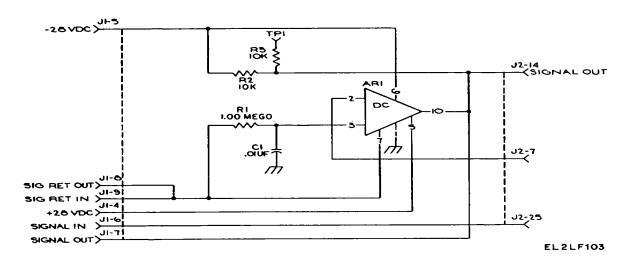

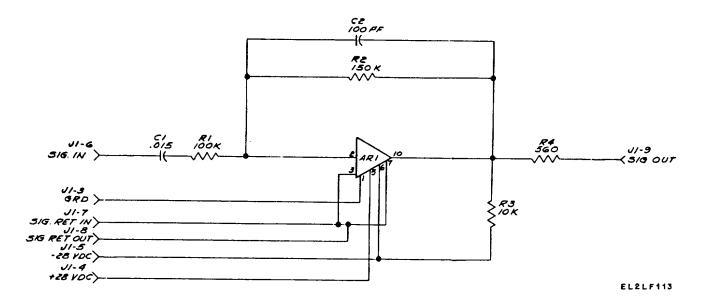

| 3-13   | DC amplifier ARI, schematic diagram                                   |      |

| 3-14   | Gate expander 1A2A5A23A27, schematic diagram                          | 3-15 |

| 3-15   | Dual NAND gate 1A2A5A23A28, schematic diagram                         | 3-15 |

|        |                                                                       |      |

<sup>\*</sup>This manual supersedes TM 11-5895-389-34-2NAVSHIPS 0967-377-7020tO 31RS-2TSC54-22, 12 February 1971.

| Figure               |                                                                                 | Page         |

|----------------------|---------------------------------------------------------------------------------|--------------|

| 3-16                 | NAND gate 1A2A5A23A29, schematic diagram                                        | 3-16         |

| 3-17                 | NAND gate driver 1A2A5A23A31, schematic diagram                                 |              |

| 3-18                 | Operational amplifier 1A2A5A23A61, schematic diagram                            |              |

| 3-19                 | Level shifter 1A2A5A23A63, schematic diagram                                    |              |

| 3-20                 | Dual low level switch 1A2A5A23A76, schematic diagram                            |              |

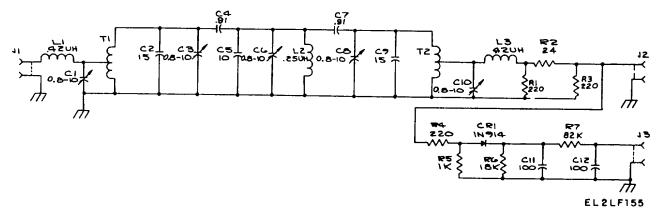

| 3-21                 | 70 MHz shaping circuit 1A2A5A24A1, schematic diagram                            | 3-20         |

| 3-22                 | Line driver 1A2A5A24A44, schematic diagram                                      | 3-20         |

| 3-23                 | Impedance amplifier 1A2A5A24A45, schematic diagram                              | 3-21         |

| 3-24                 | Variable time delay 1A2A5A24A47, schematic diagram                              | 3-21         |

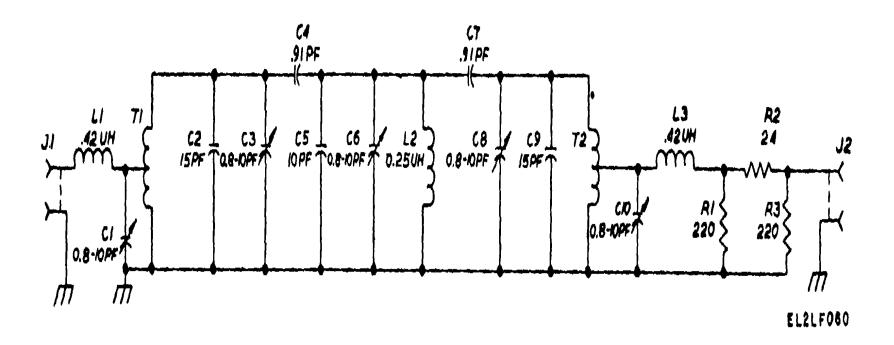

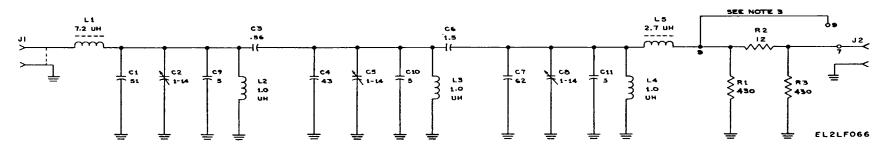

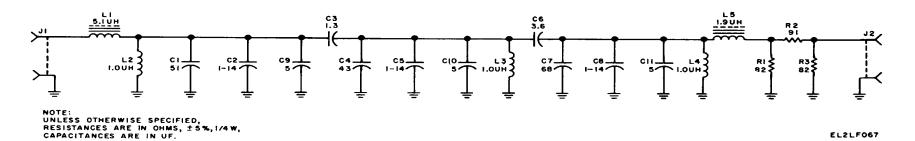

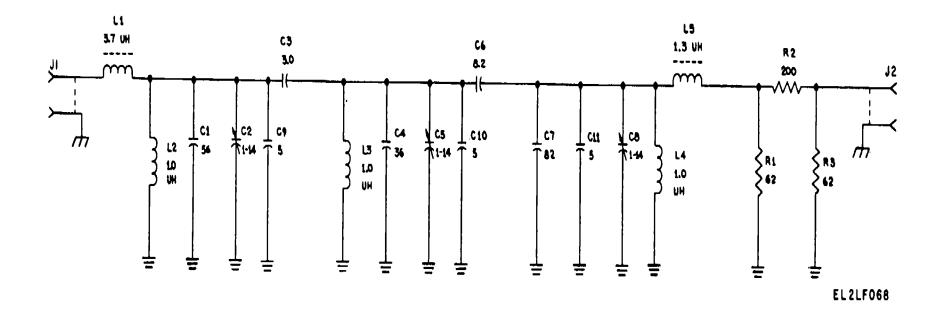

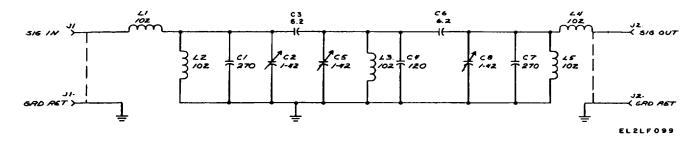

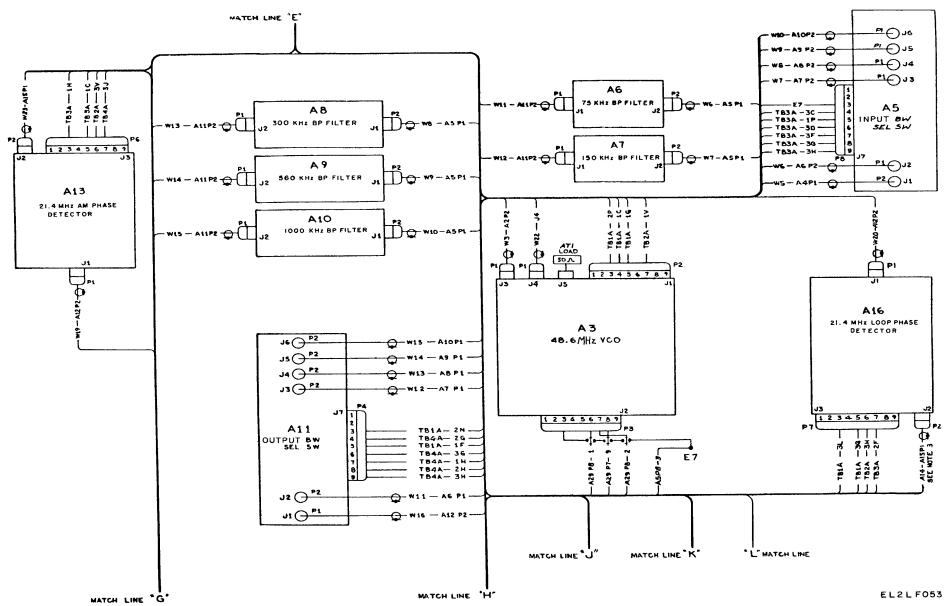

| 3-25                 | 70 MHz bandpass filter 1A3A3A1, schematic diagram                               | 3-24         |

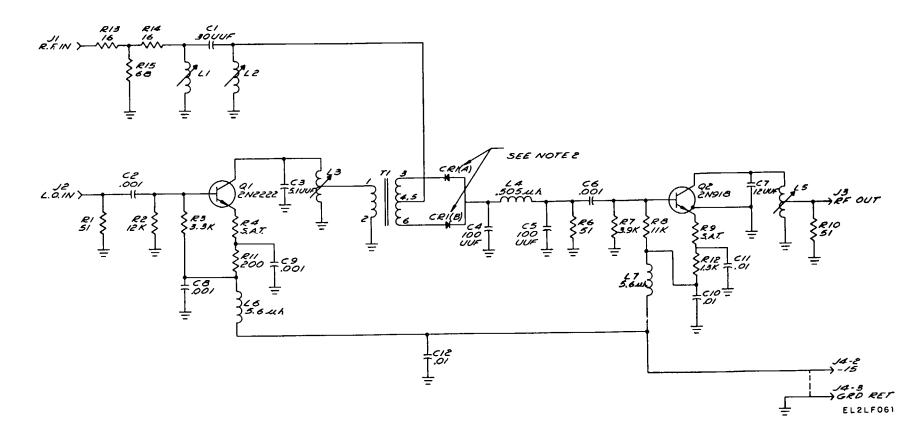

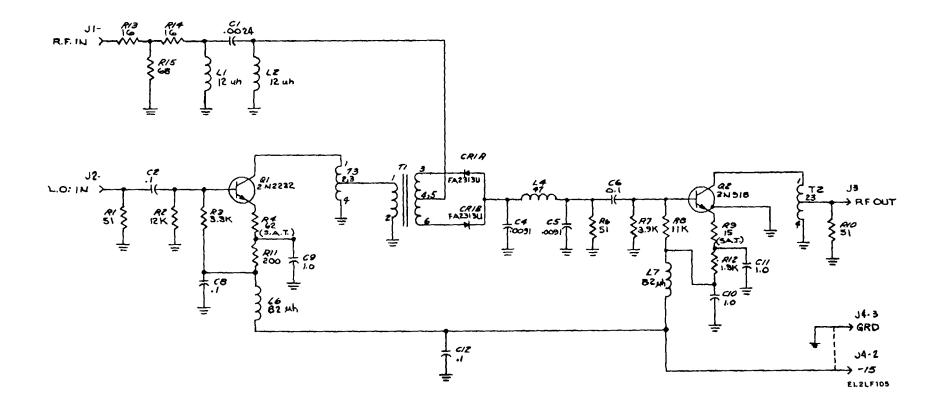

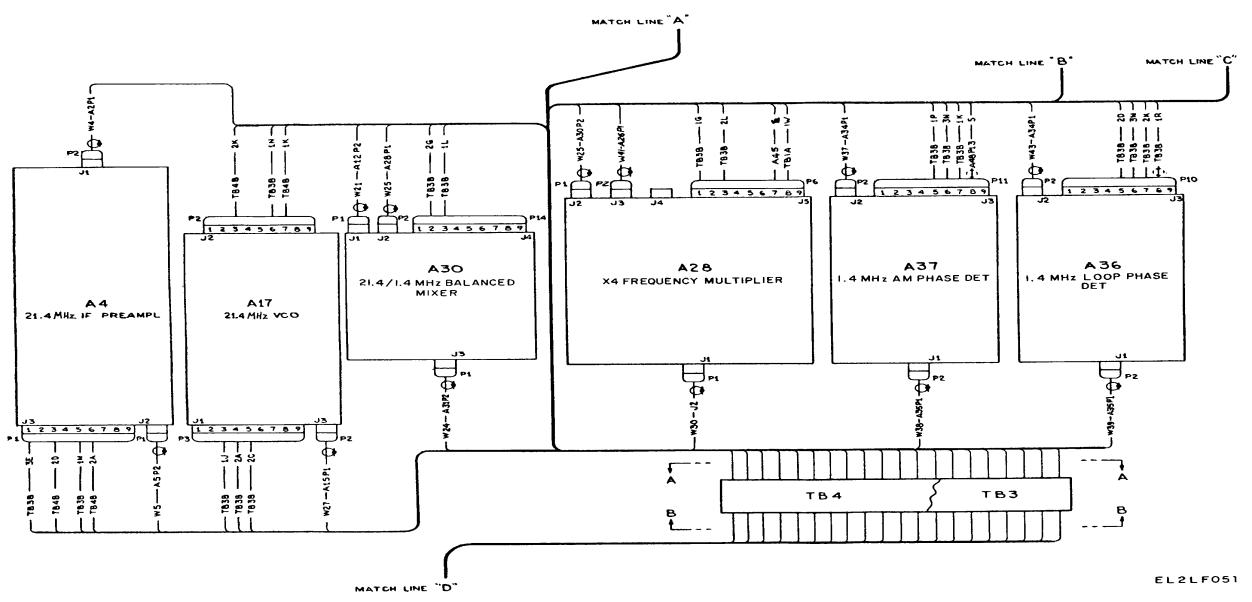

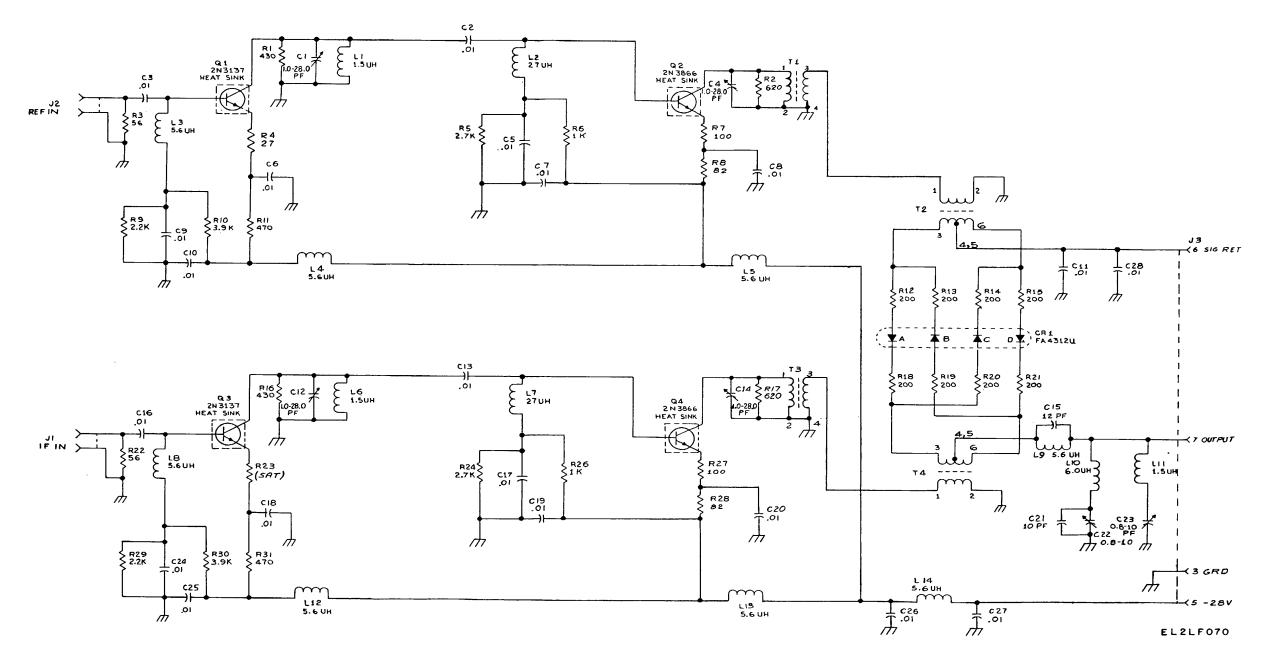

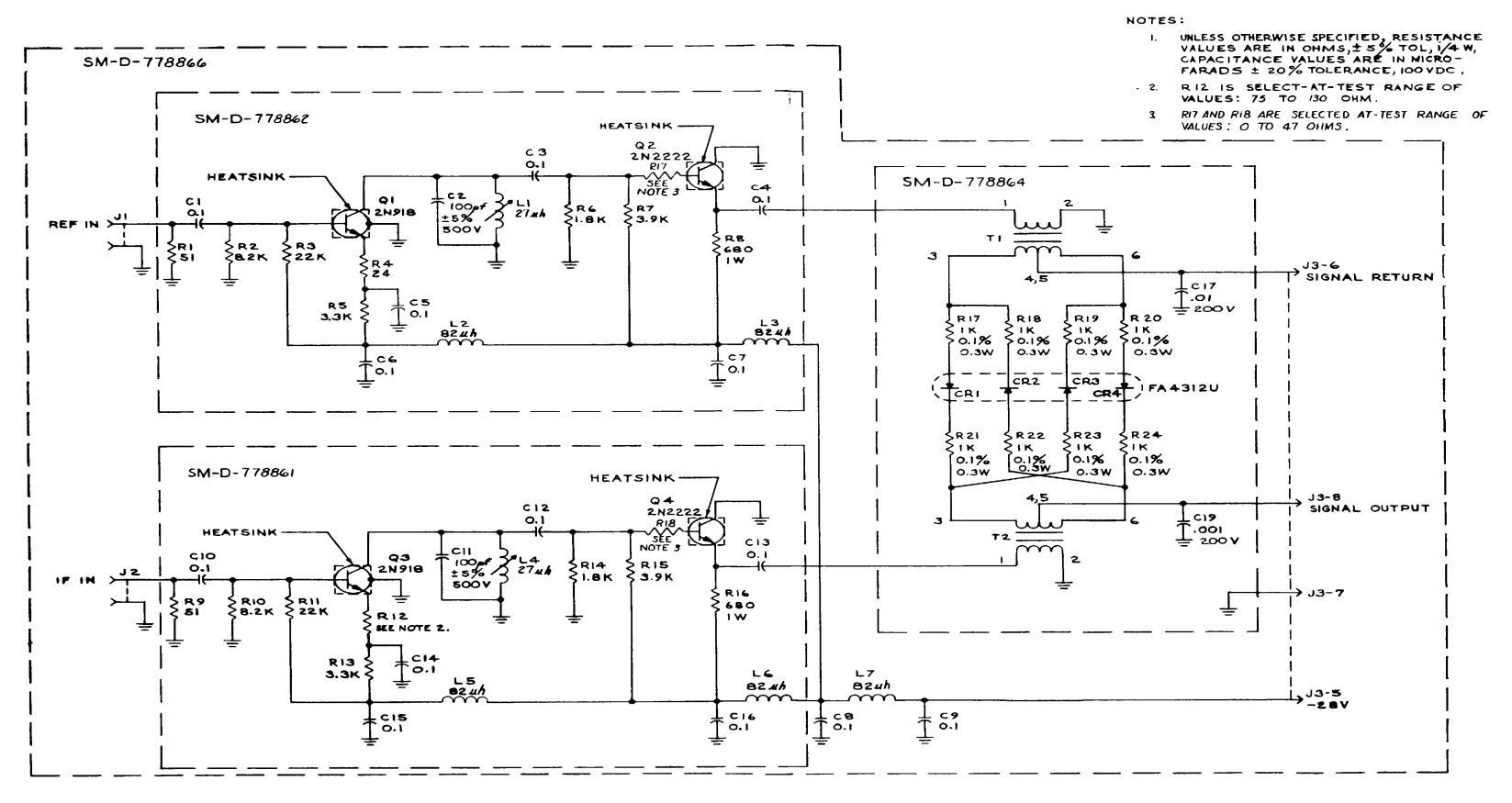

| 3-26                 | 70 MHz to 21.4 MHz balanced mixer 1A3A3A2, schematic diagram                    | 3-25         |

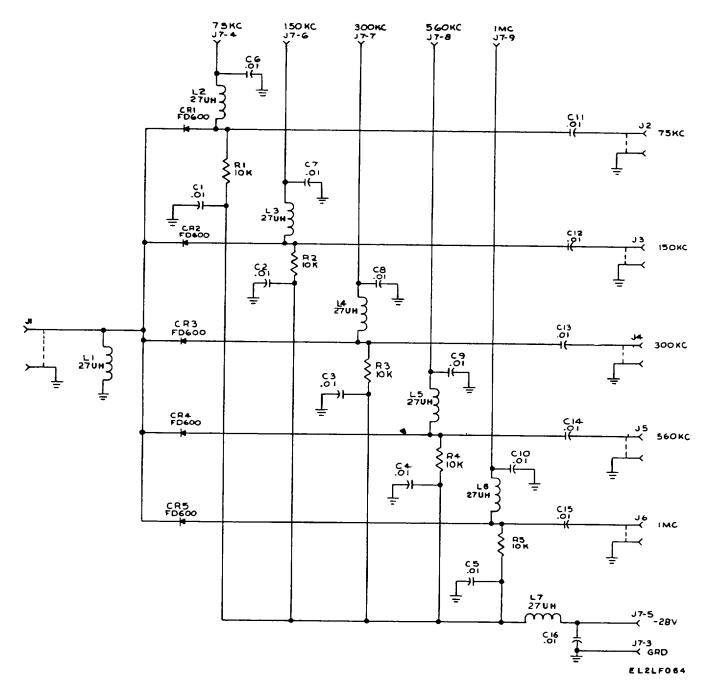

| 3-27                 | Signal bandwidth select switch 1A3A3A5, schematic diagram                       | 3-26         |

| 3-28                 | 75 kHz bandpass filter 1A3A3A6, schematic diagram                               | 3-27         |

| 3-29                 | 300 kHz bandpass filter 1A3A3A8, schematic diagram                              | 3-29         |

| 3-30                 | 560 kHz bandpass filter 1A3A3A9, schematic diagram                              | 3-29         |

| 3-31                 | 1000 kHz bandpass filter 1A3A3A10, schematic diagram                            | 3-30         |

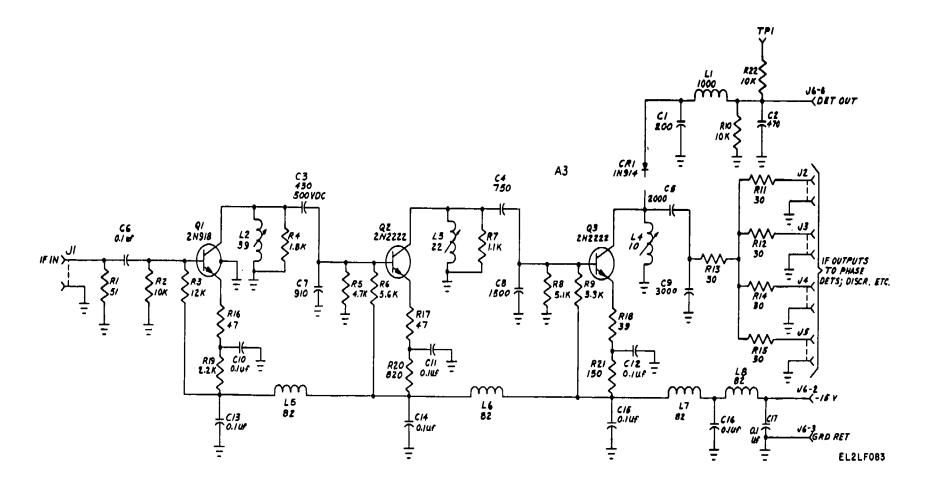

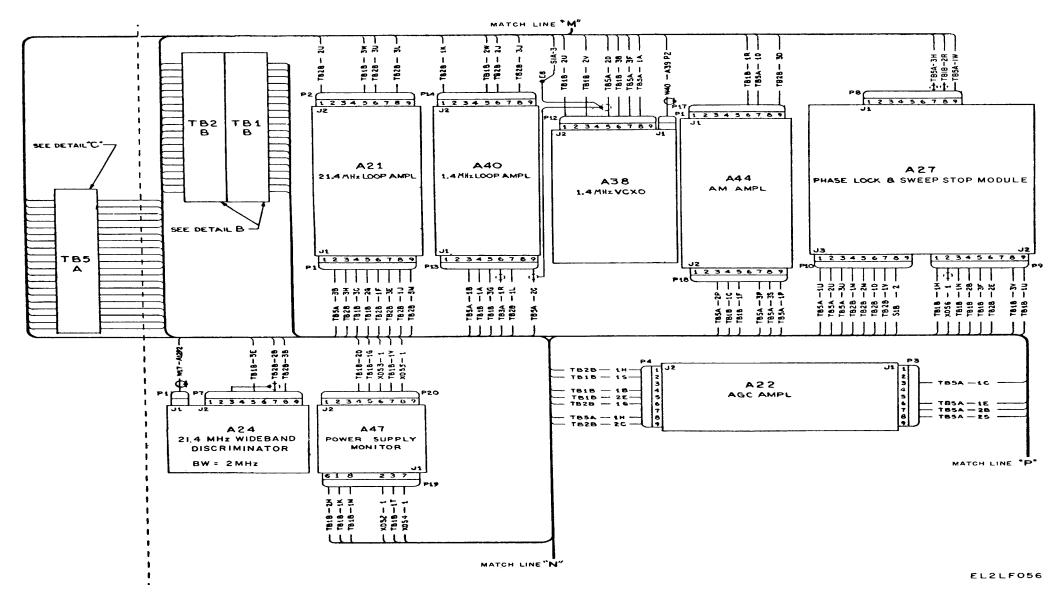

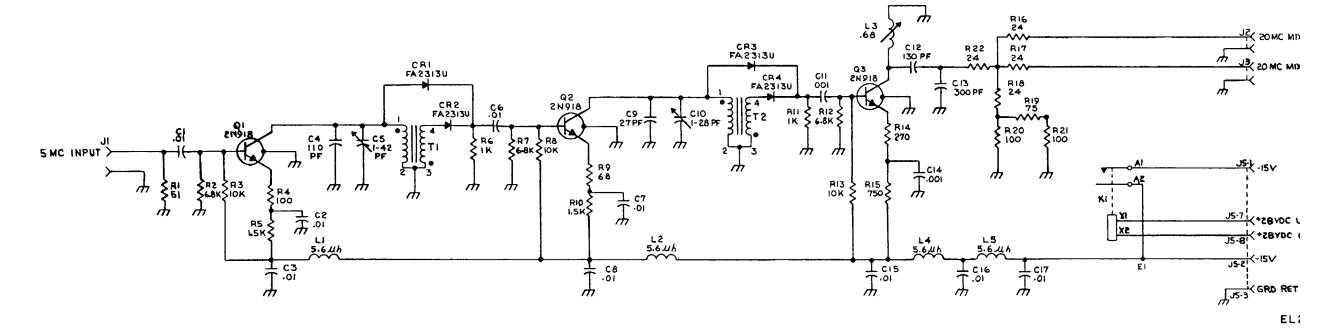

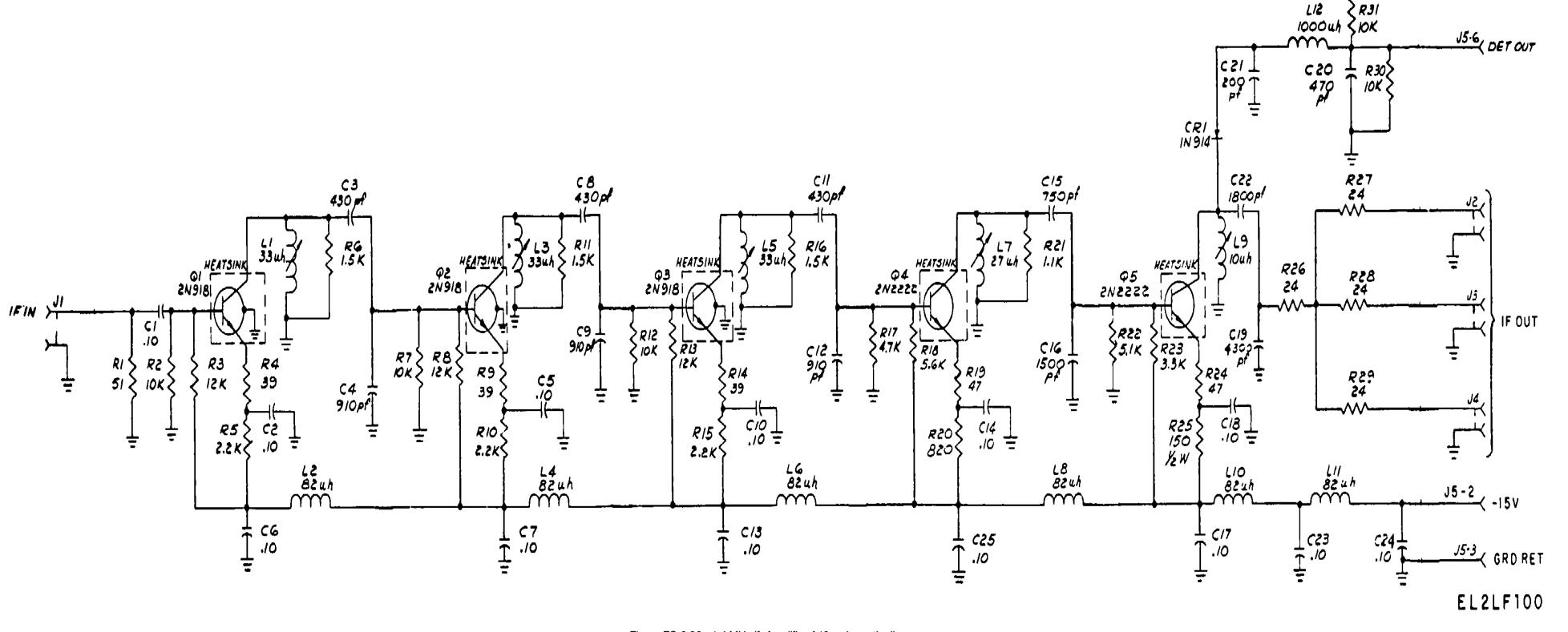

| 3-32                 | 21.4 MHz and 1.4 MHz loop amplifiers 1A3A3A21, schematic diagram                | 3-31         |

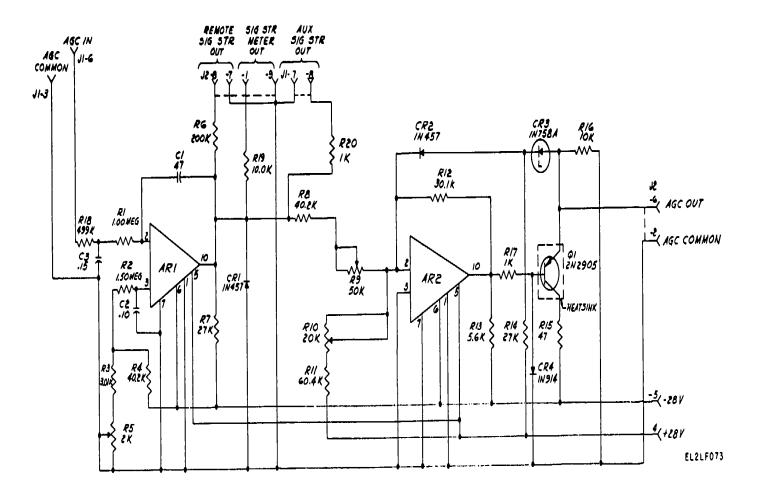

| 3-33                 | AGC amplifier 1A3A3A22, schematic diagram                                       |              |

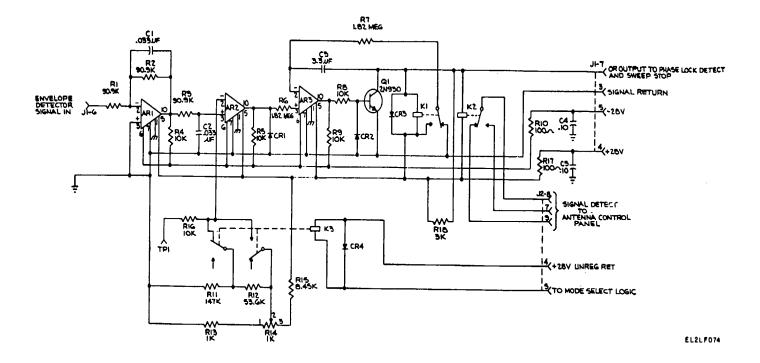

| 3-34                 | Demod signal detector 1A3A3A23, schematic diagram                               | 3-34         |

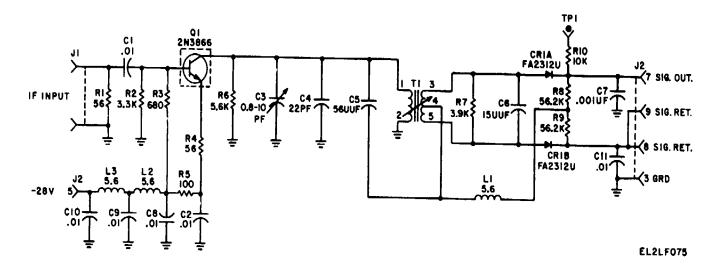

| 3-35                 | 21.4 MHz wideband discriminator 1A3A3A24, schematic diagram                     |              |

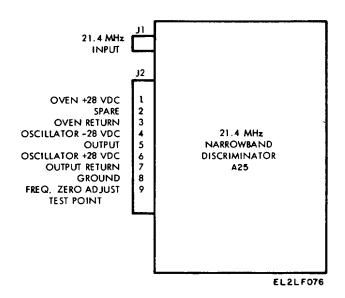

| 3-36                 | 21.4 MHz narrowband discriminator 1A3A3A25, input/output signal characteristics | 3-35         |

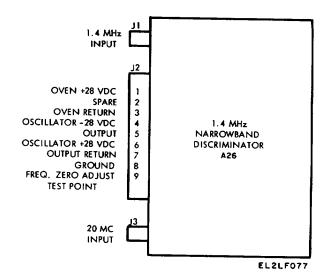

| 3-37                 | 1.4 MHz narrowband discriminator 1A3A3A26, input/output signal characteristics  |              |

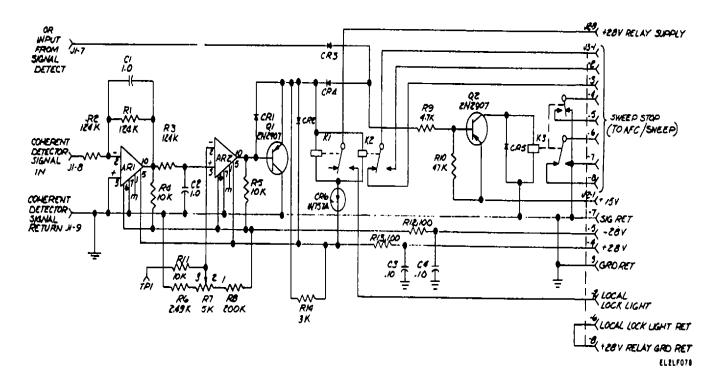

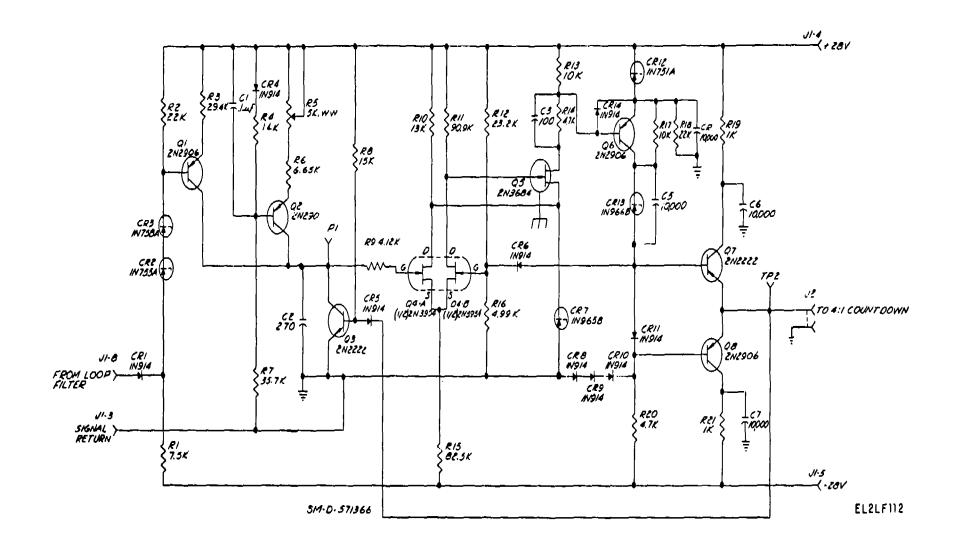

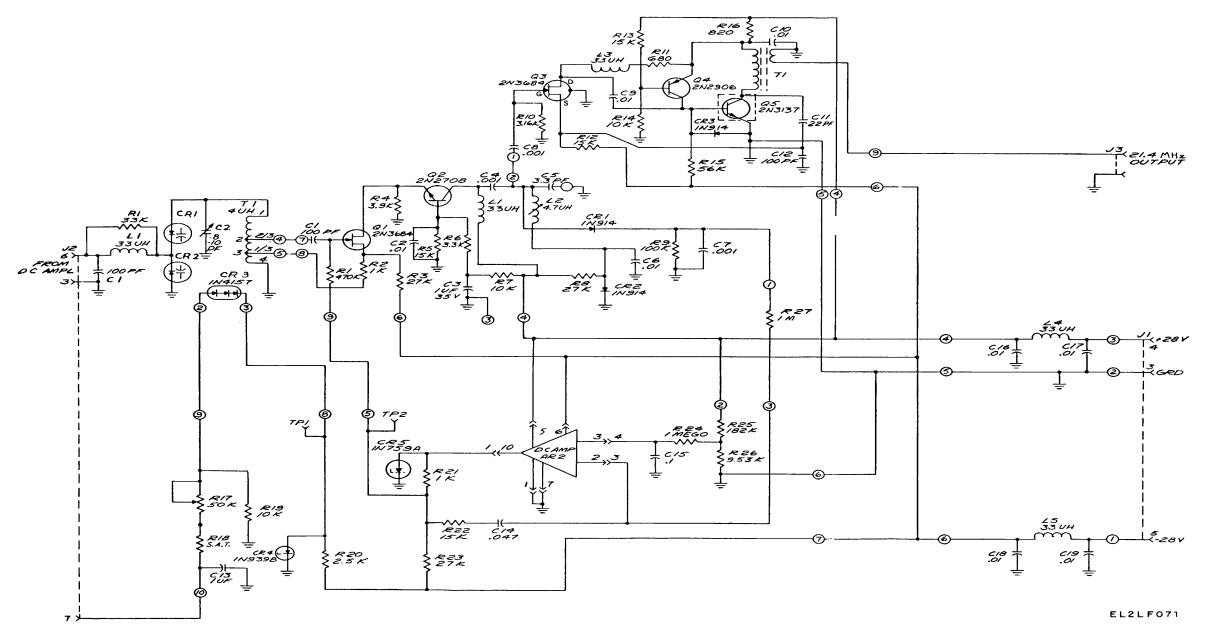

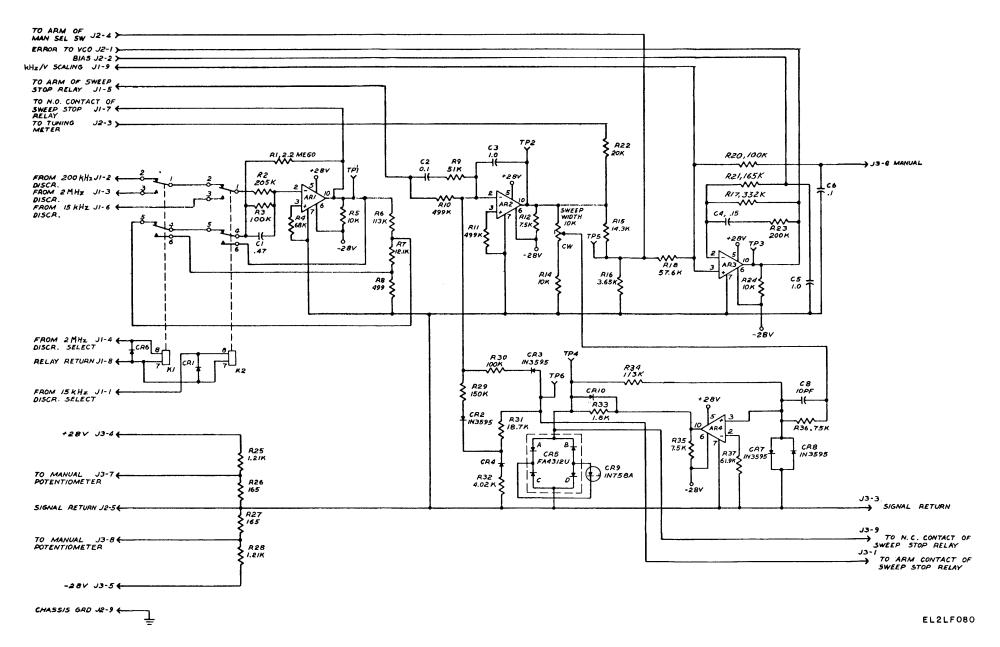

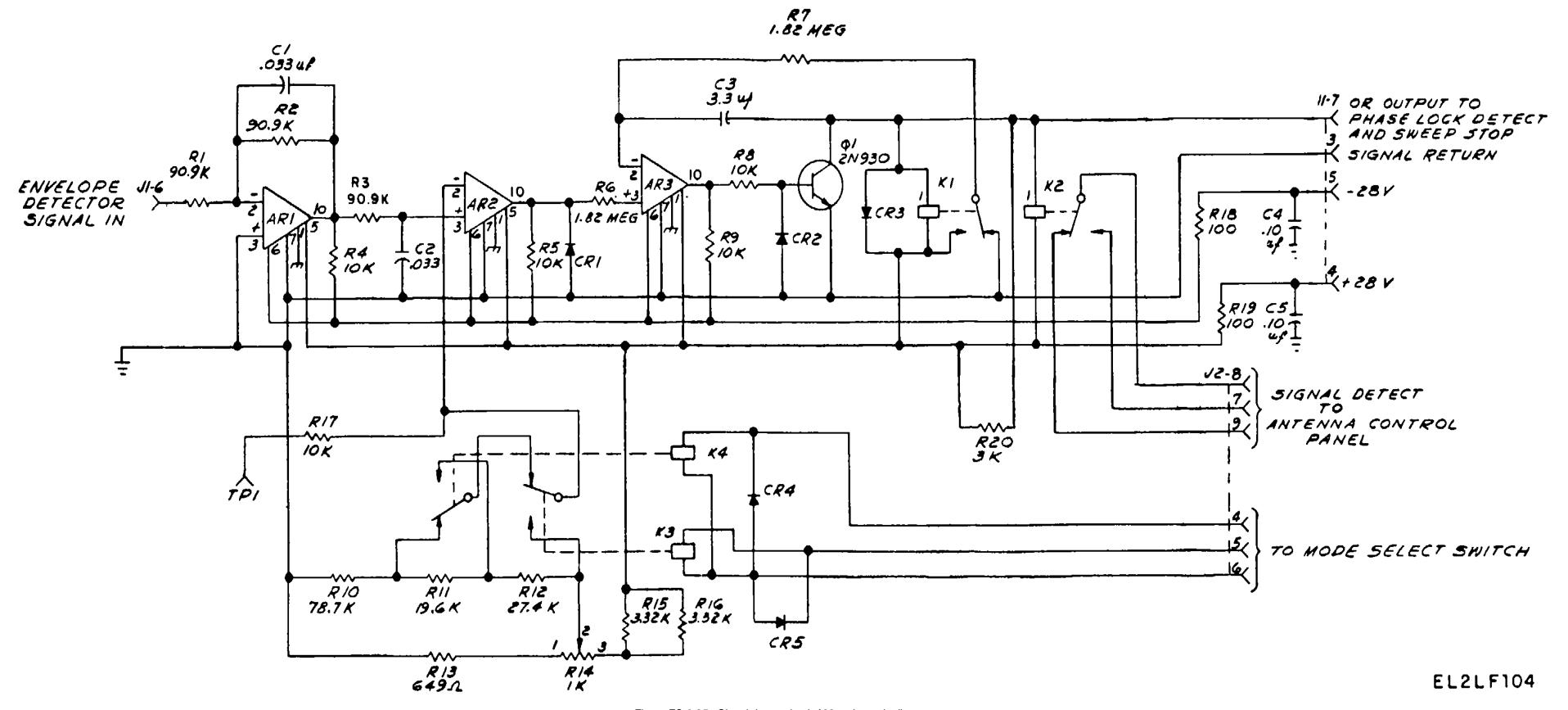

| 3-38                 | Phase lock and sweep stop circuit 1A3A3A27, schematic diagram                   | 3-38         |

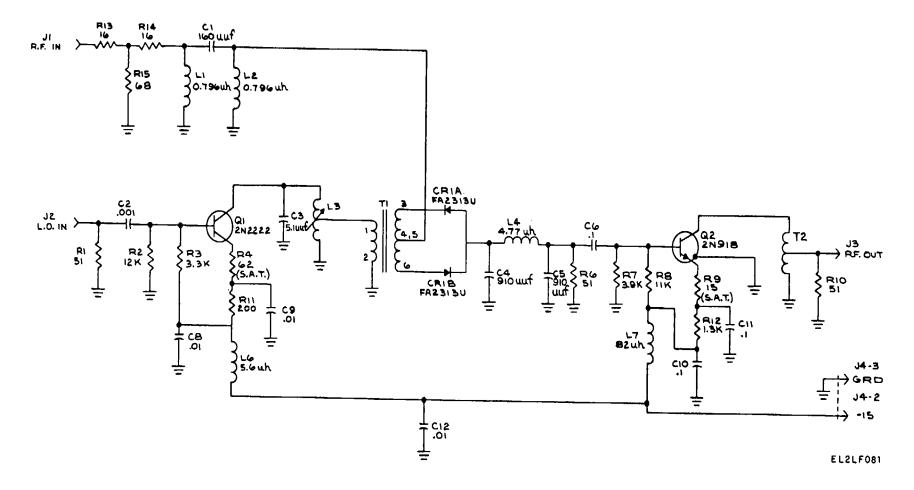

| 3-39                 | 21.4 MHz to 1.4 MHz balanced mixer 1A3A3A30, schematic diagram                  | 3-39         |

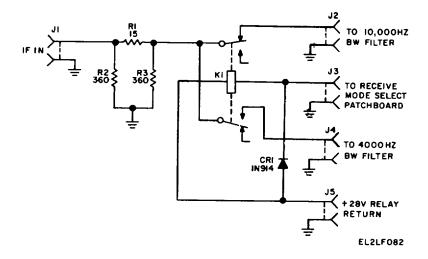

| 3-40                 | 1.4 MHz if. bandwidth select circuit 1A3A3A46, schematic diagram                |              |

| 3-41                 | 1.4 MHz post amplifier 1A3A3A34, schematic diagram                              | 3-42         |

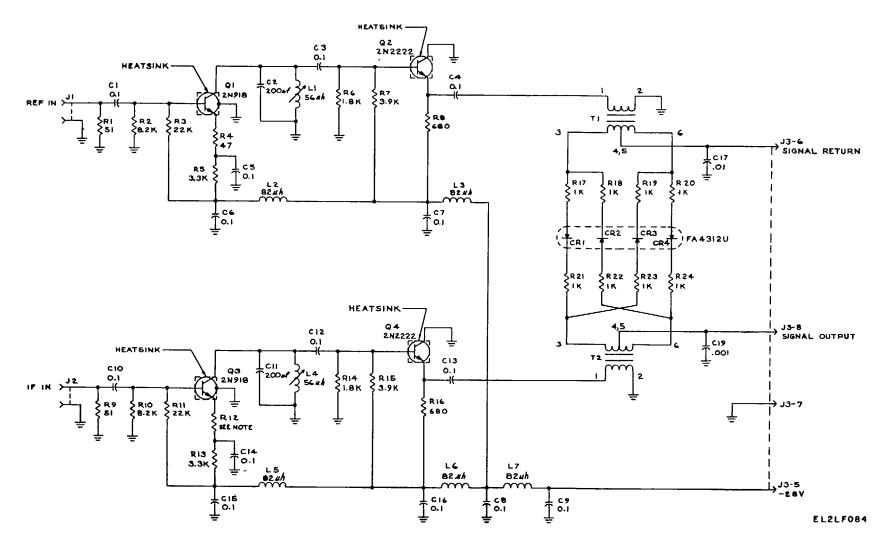

| 3-42                 | 1.4 MHz loop phase detector 1A3A3A36, schematic diagram                         | 3-43         |

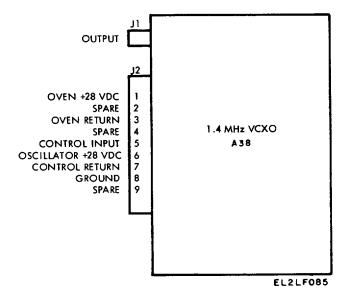

| 3-43                 | 1.4 MHz VCXO 1A3A3A38, input/output signal characteristics                      | 3-44         |

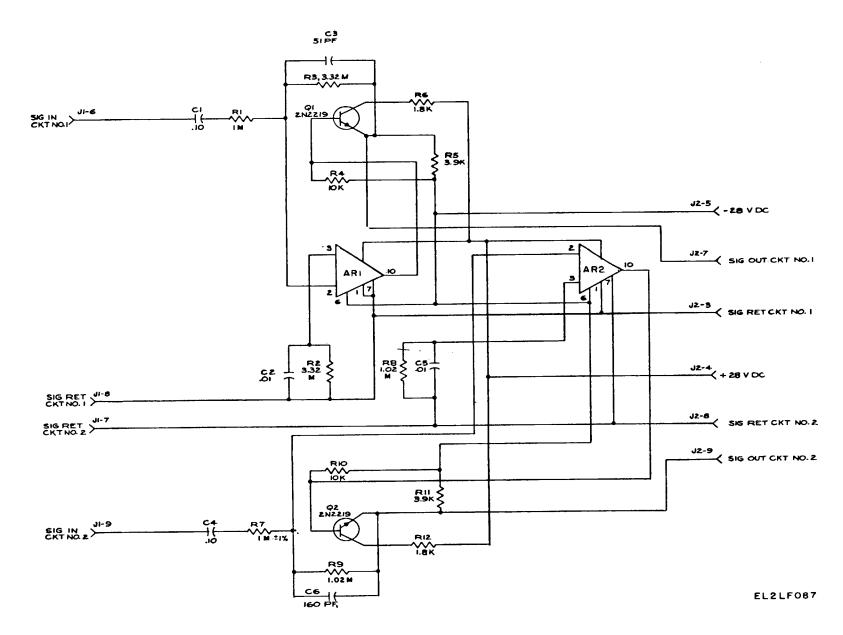

| 3-44                 | AM amplifier 1A3A3A44, schematic diagram                                        | 3-45         |

| 3-45                 | Power supply monitoring circuits 1A3A3A47, schematic diagram                    |              |

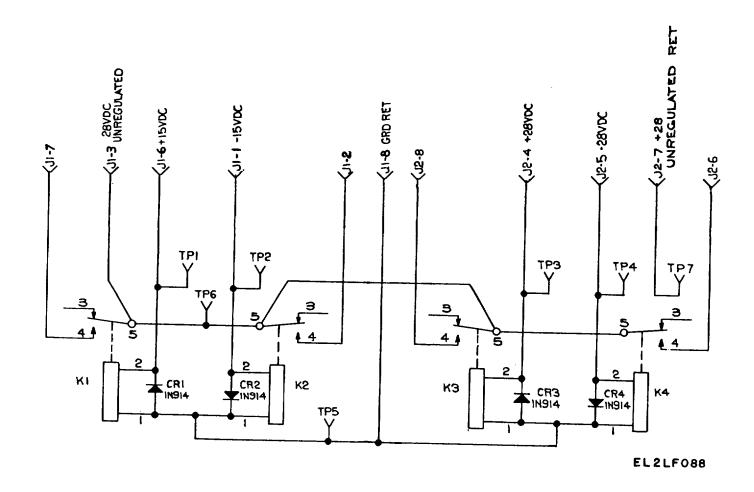

| 3-46                 | Relay A48, schematic diagram                                                    |              |

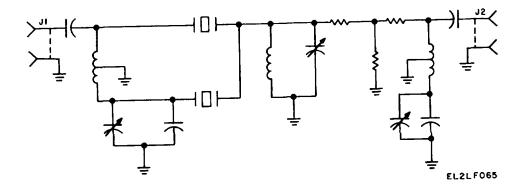

| 3-47                 | 50 kHz bandwidth filter 1A3A4A6, schematic diagram                              |              |

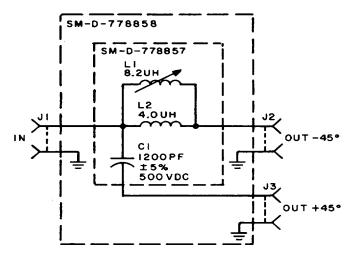

| 3-48                 | 90 degree differential phase shifter 1A3A4A17, schematic diagram                |              |

| 3-49                 | 2.8 MHz loop amplifier 1A3A4A20, schematic diagram                              |              |

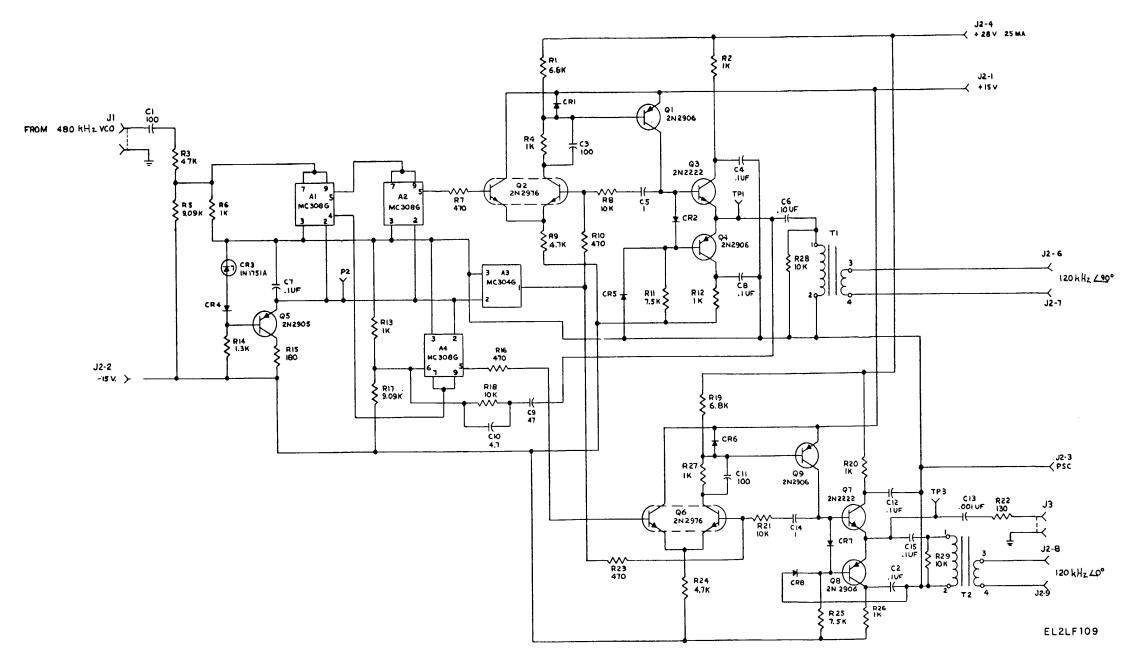

| 3-50                 | 1.28 MHz/120 kHz balanced mixer 1A3A4A25, schematic diagram                     | 3-51         |

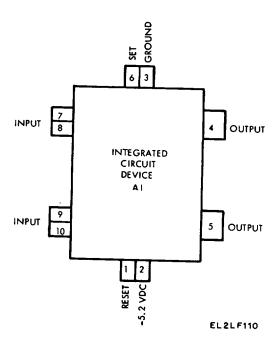

| 3-51                 | Integrated circuit device AI and A2, input and output characteristics           | 3-56         |

| 3-52                 | Integrated circuit device, schematic diagram                                    |              |

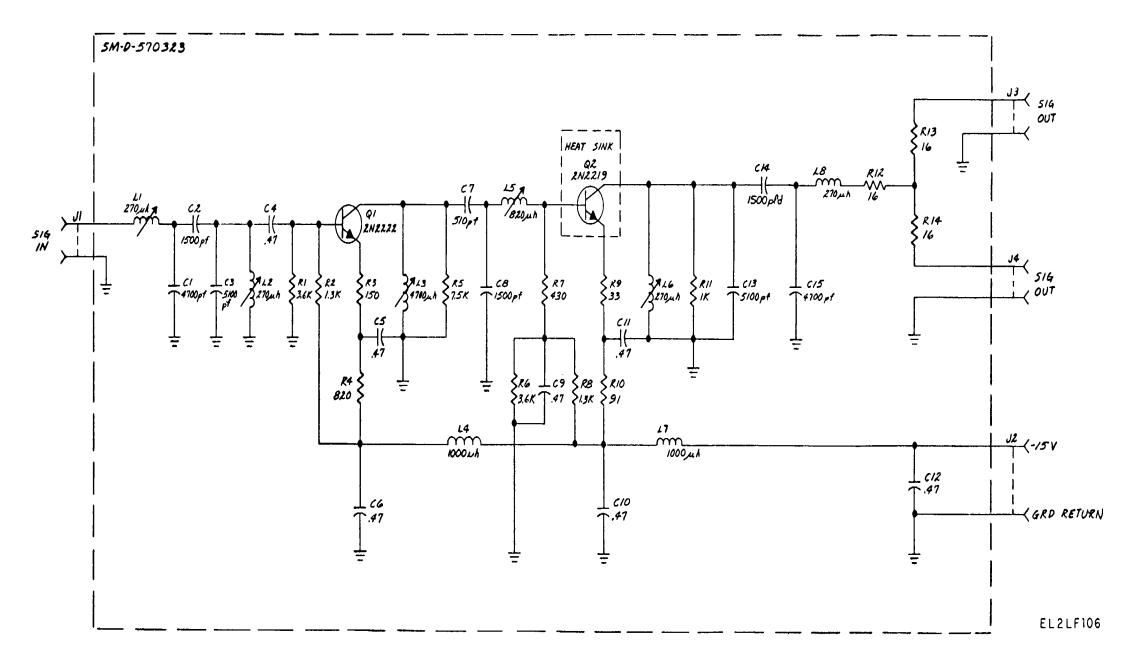

| 3-53                 | 480 kHz vco 1A3A4A31, schematic diagram                                         |              |

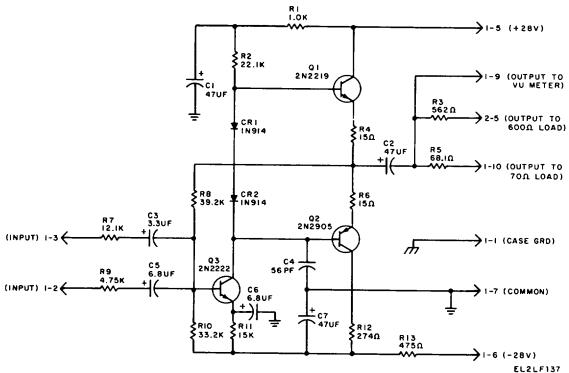

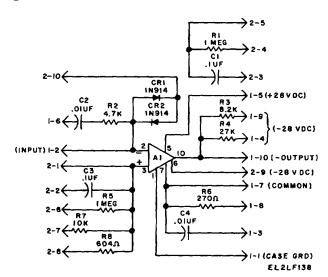

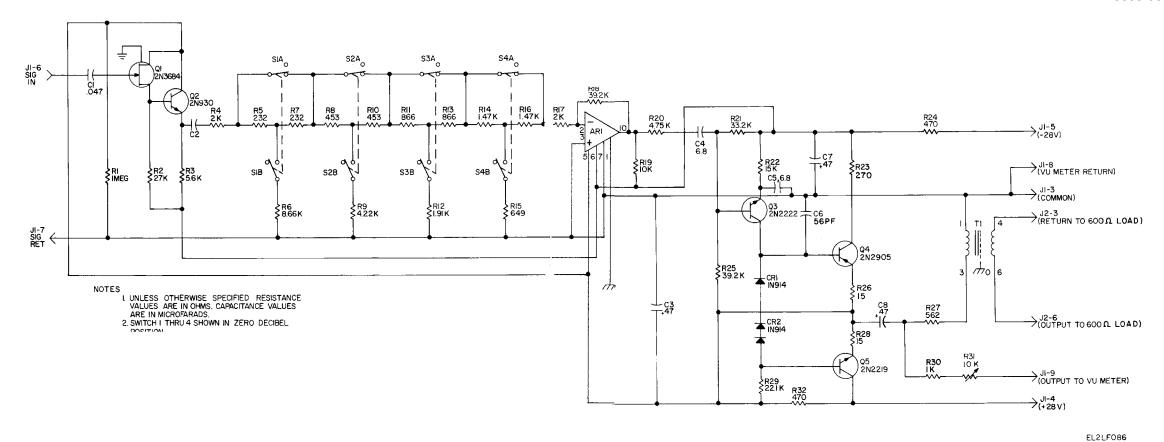

| 3-54                 | Audio amplifier 1A3A4A32, schematic diagram                                     |              |

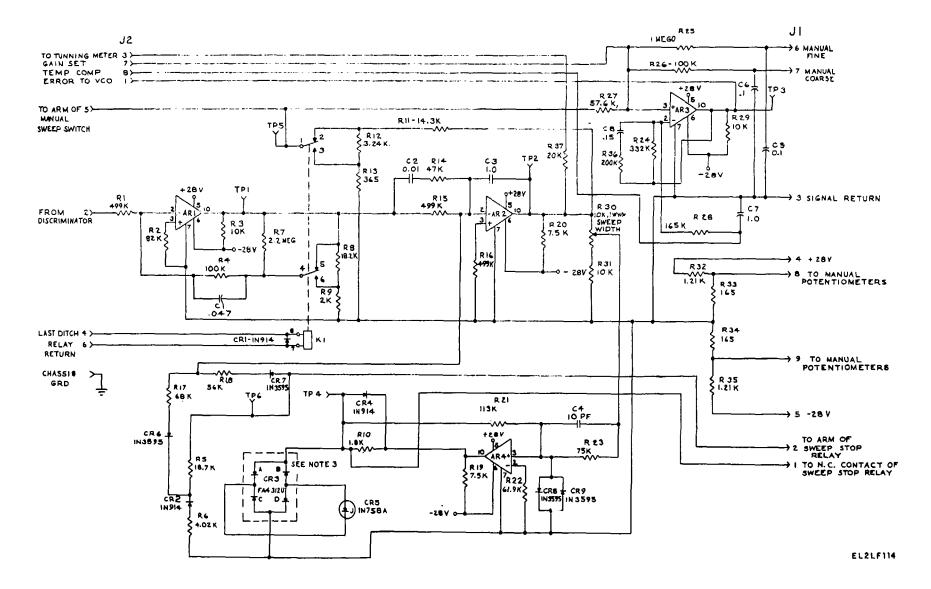

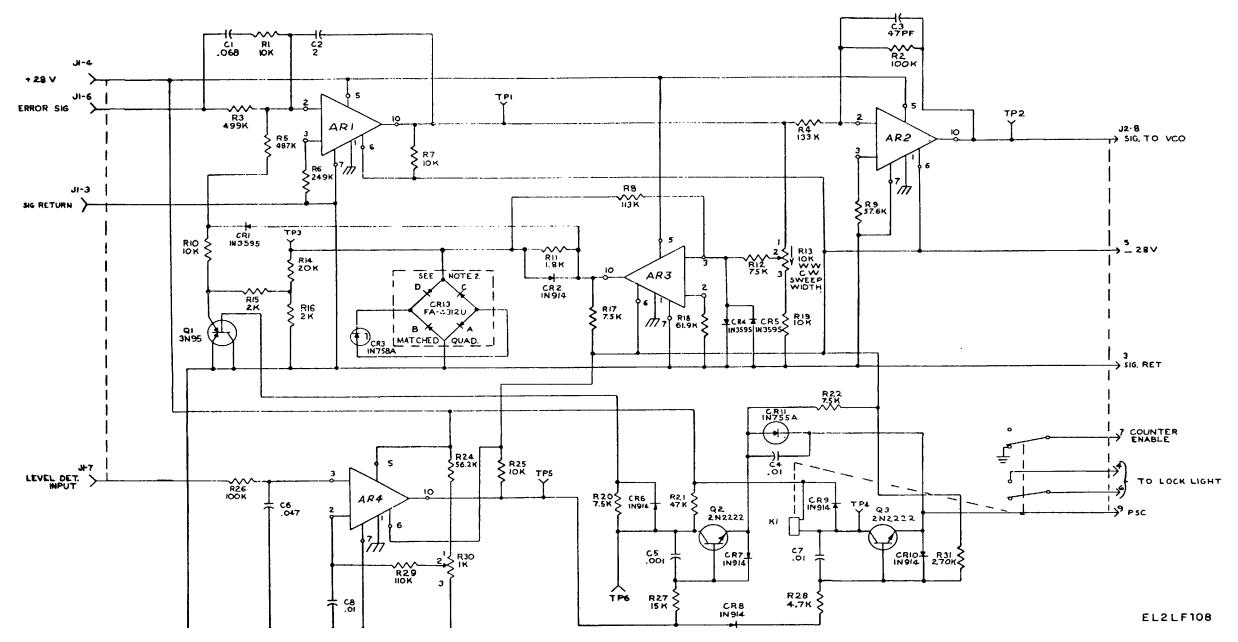

| 3-55<br>3-56         | AFC and sweep amplifier circuit 1A3A4A34, schematic diagram                     |              |

| 3-56①                |                                                                                 |              |

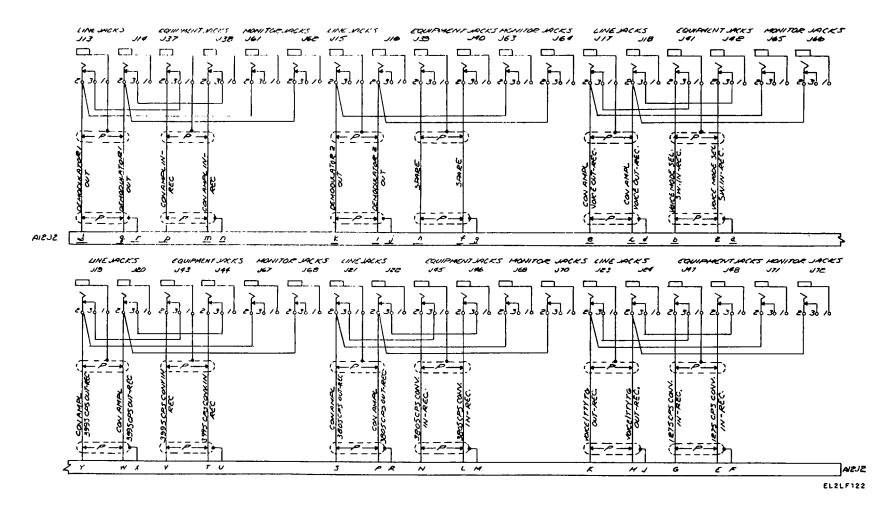

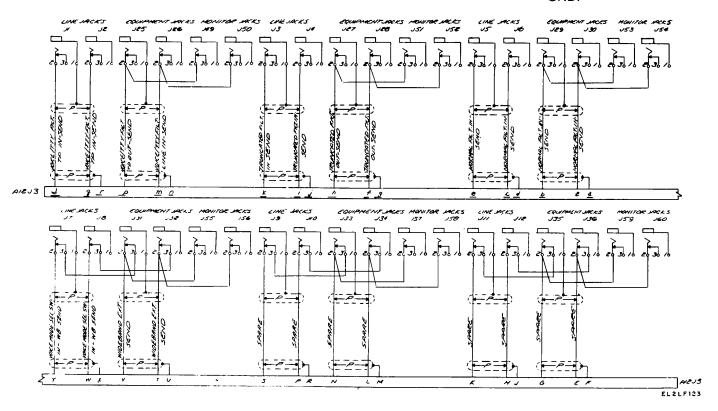

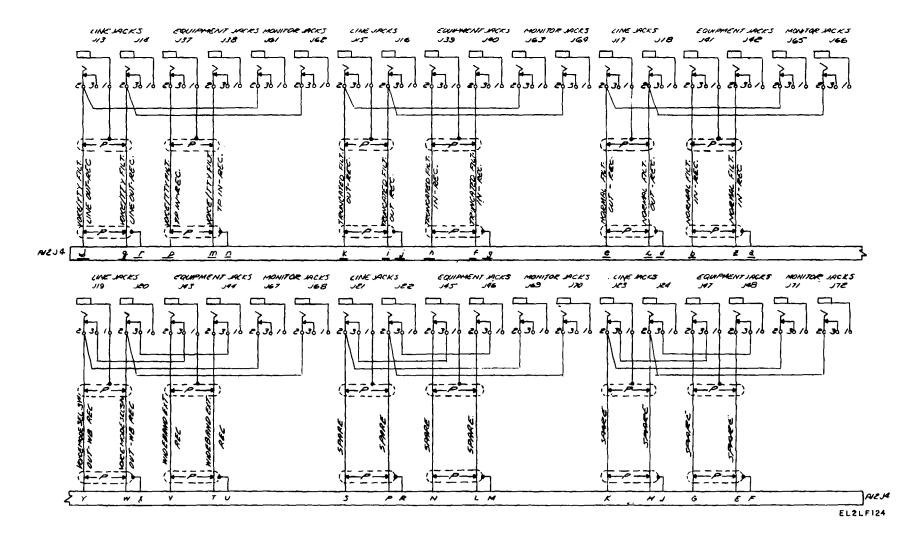

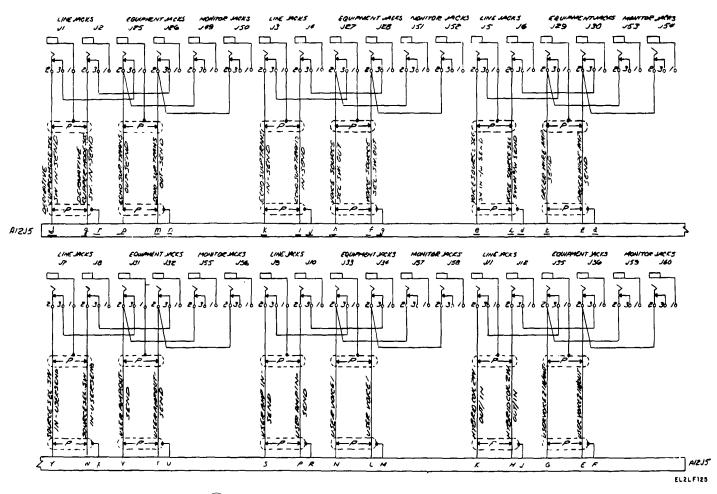

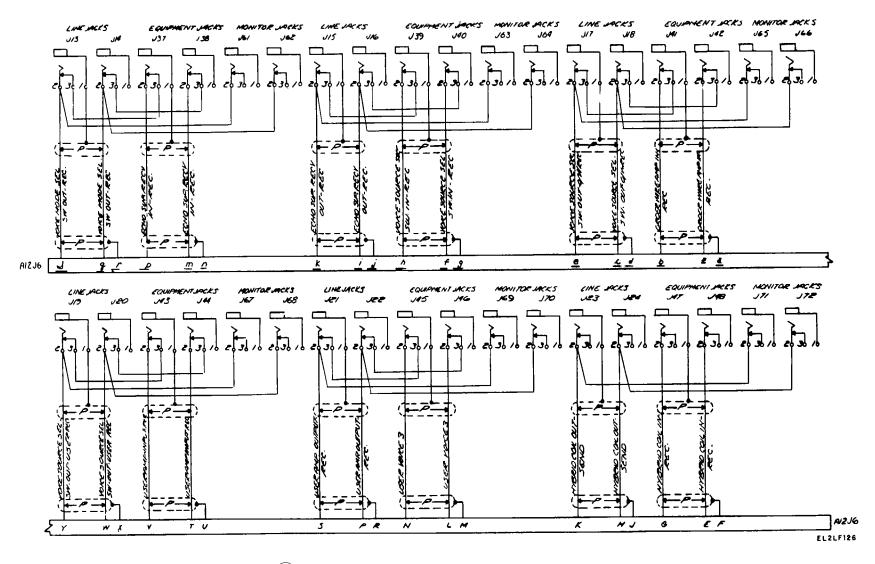

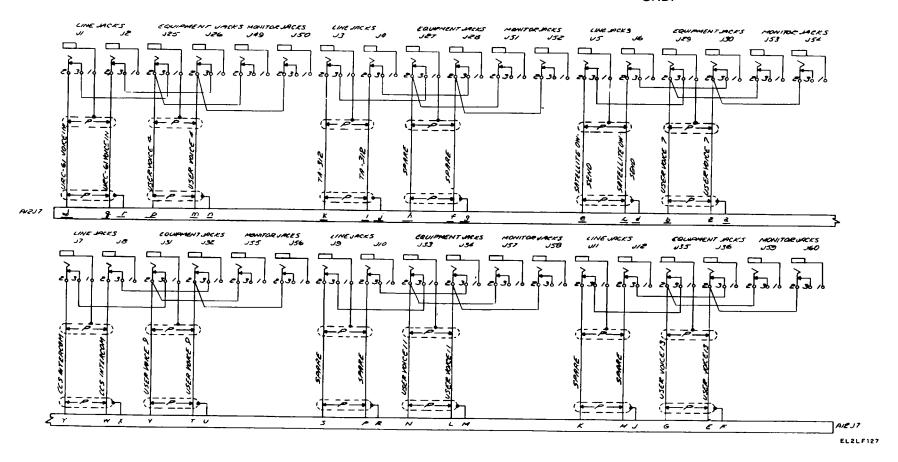

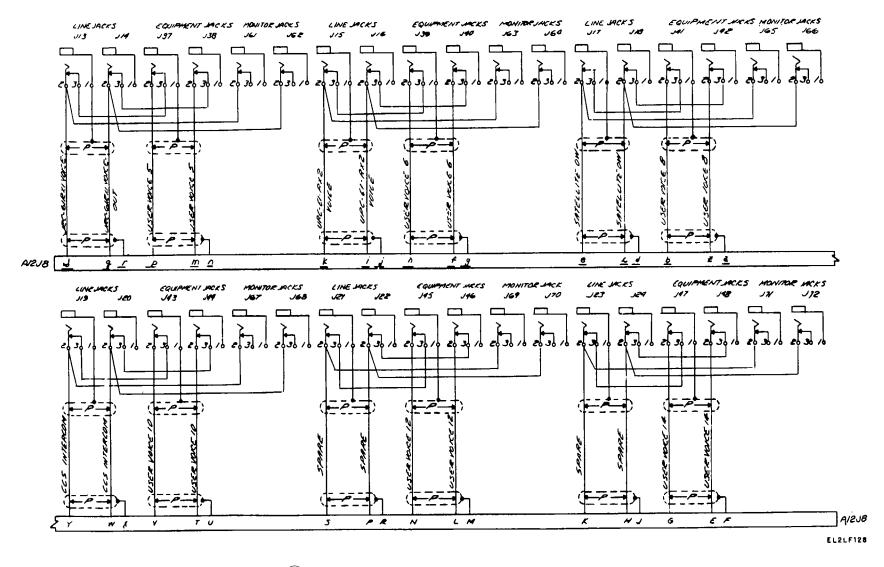

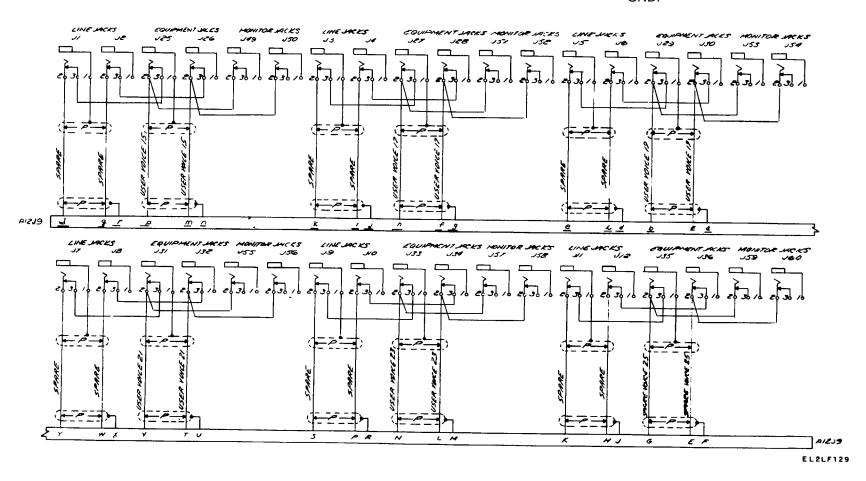

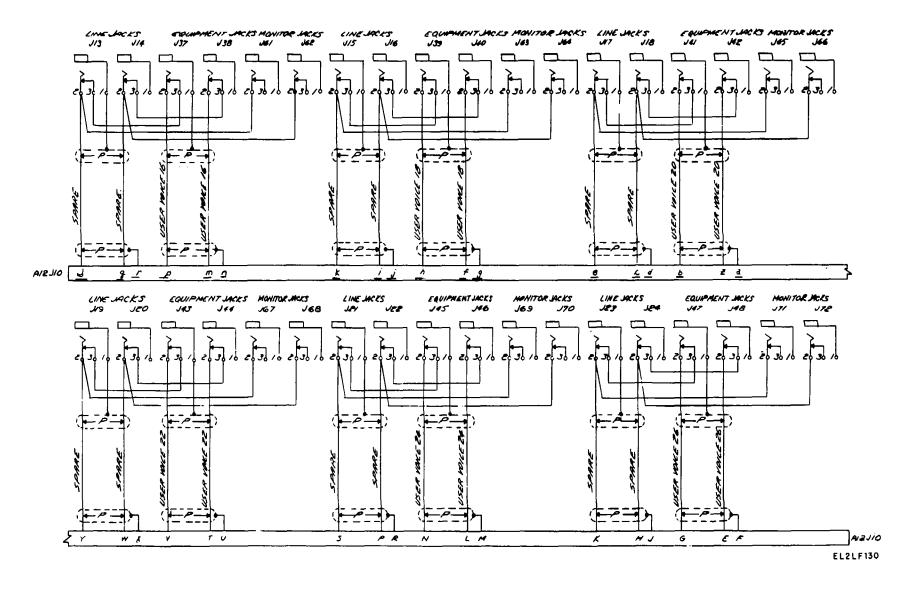

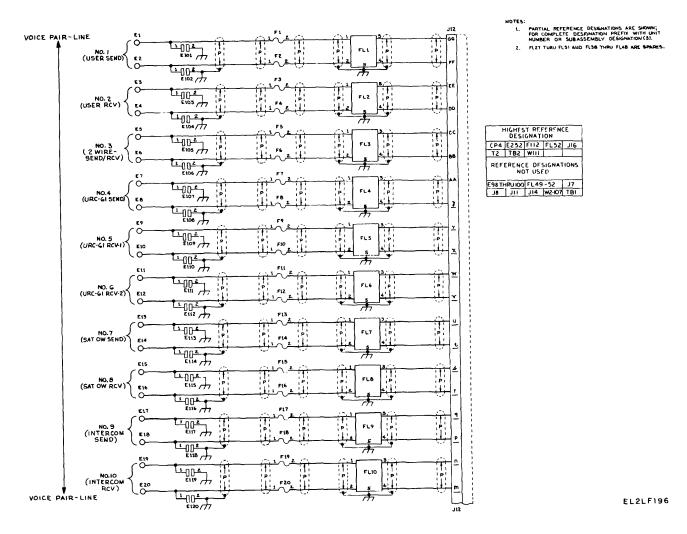

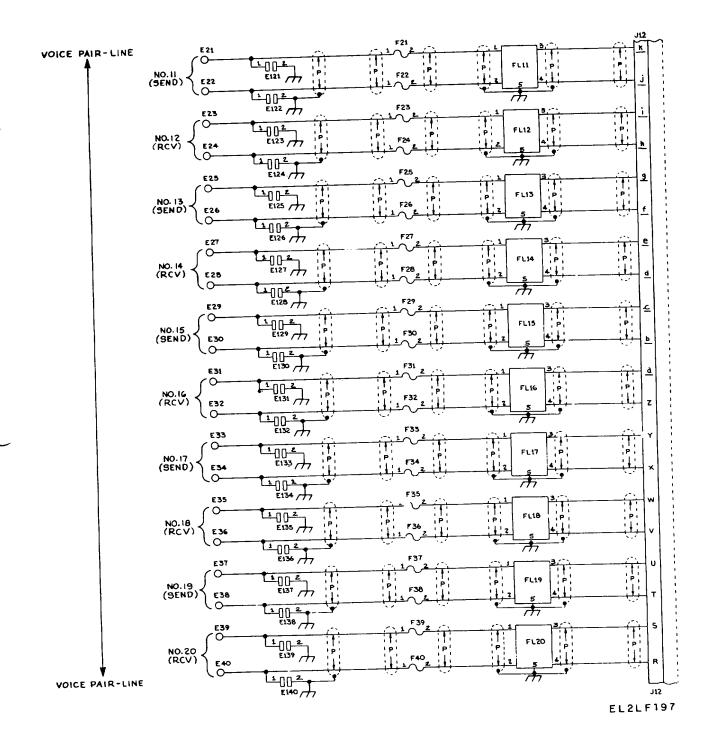

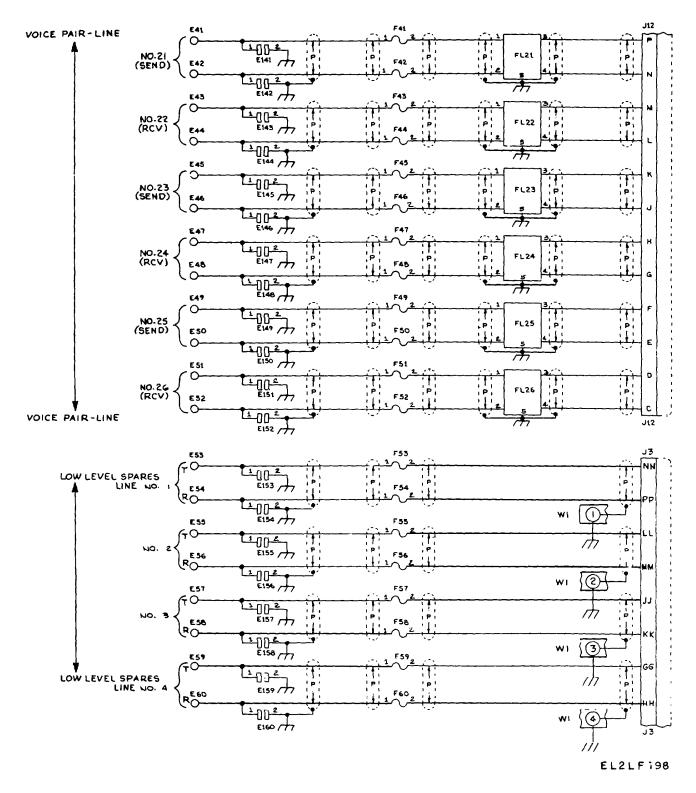

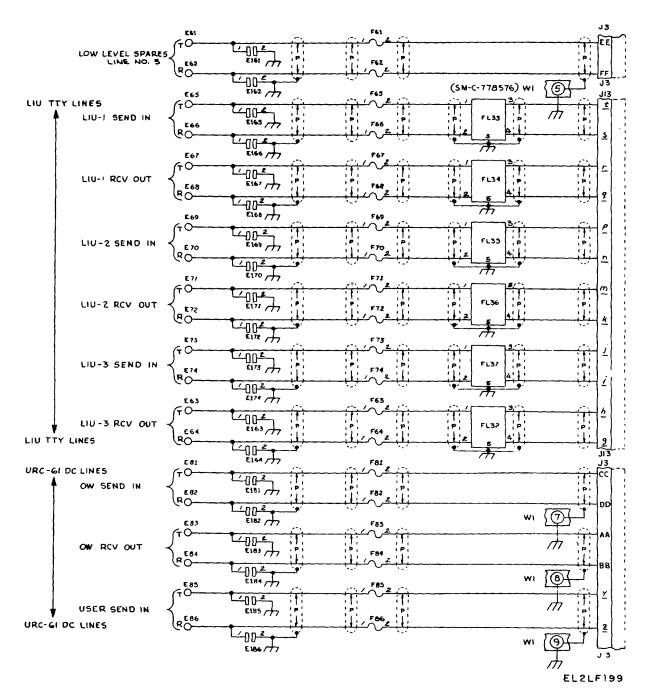

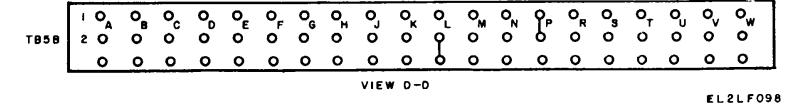

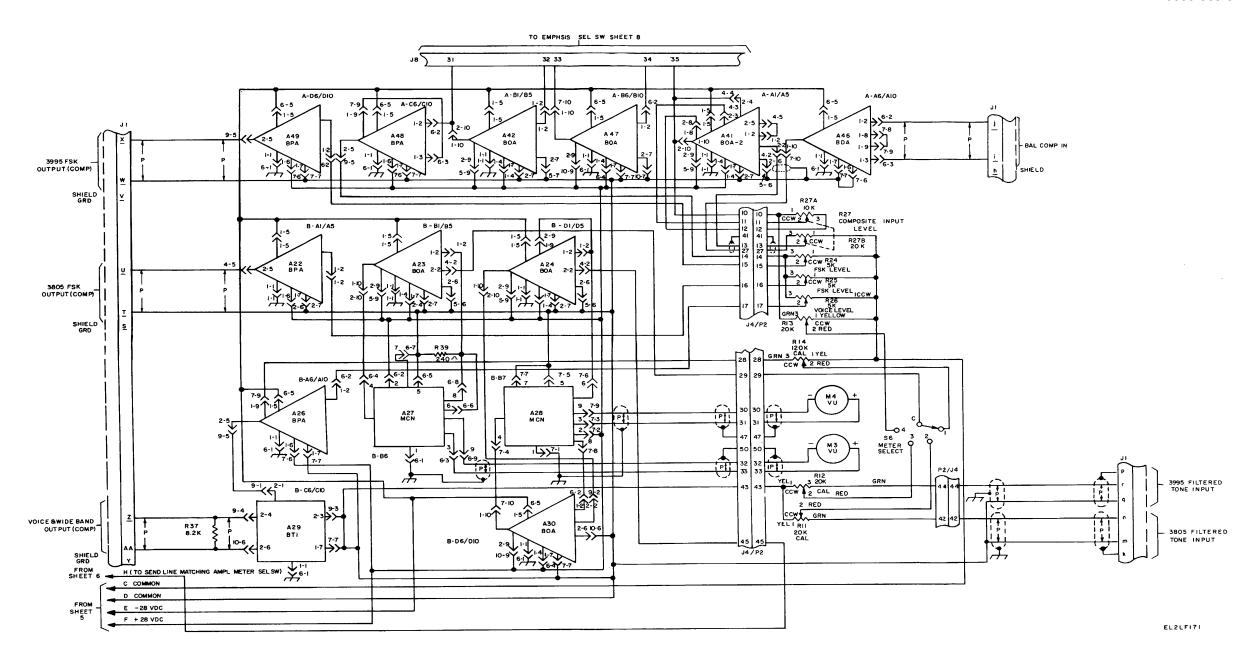

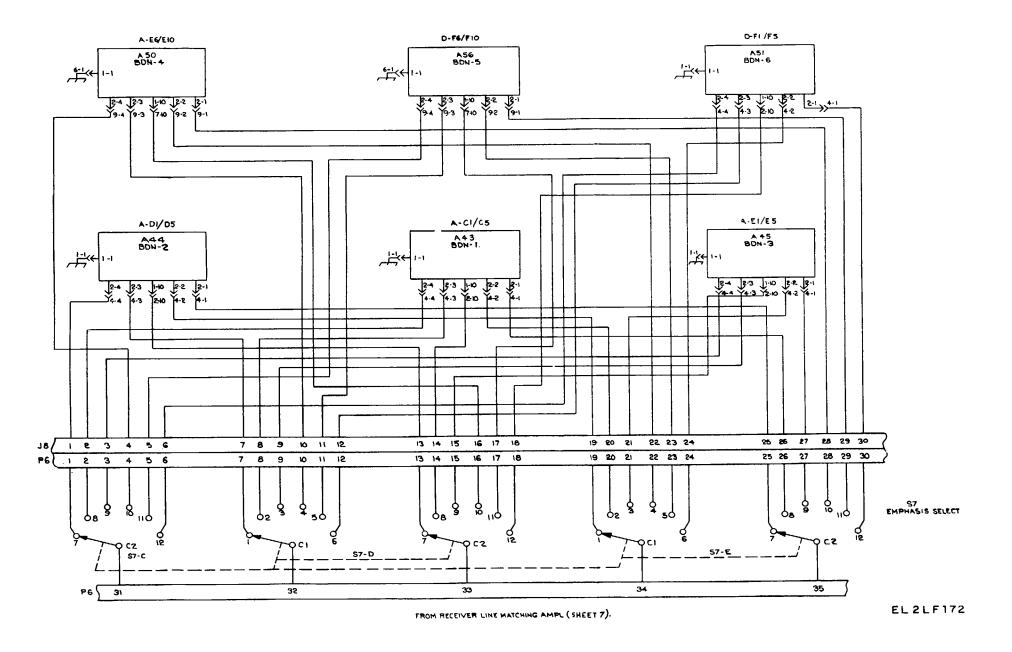

| 3-56©                | Baseband patch panel 1A3A12, wiring diagram (sheet 2 of 9)                      | 3-04<br>3-65 |

| 3-56③                | Baseband patch panel 1A3A12, wiring diagram (sheet 3 of 9)                      | ა-და<br>ა-და |

| 3-56@                | Baseband patch panel 1A3A12, wiring diagram (sheet 5 of 9)                      | 2 67         |

| 3-56©<br>3-56©       | Baseband patch panel 1A3A12, wiring diagram (sheet 6 of 9)                      | 3-01         |

| 3-56⑦                | Baseband patch panel 1A3A12, wiring diagram (sheet 7 of 9)                      |              |

| 3-56®                | Baseband patch panel 1A3A12, wiring diagram (sheet 8 of 9)                      |              |

| 3-56®                | Baseband patch panel 1A3A12, wiring diagram (sheet 9 of 9)                      |              |

| 3-50 ©<br>3-57       | Baseband power amplifier, schematic diagram                                     | 3-71         |

| 3-5 <i>1</i><br>3-58 | Baseband operational amplifier, schematic diagram                               | 3-72         |

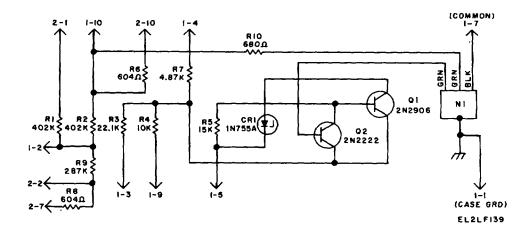

| 3-59                 | Baseband tone filter, schematic diagram                                         |              |

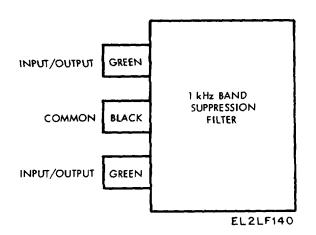

| 3-60                 | 1 kHz band suppression filter, schematic diagram                                |              |

| 3-61                 | Twin-tee network and level control circuit, schematic diagram                   |              |

| 3-62                 | Modulation amplifier 1A3A14A1, schematic diagram                                |              |

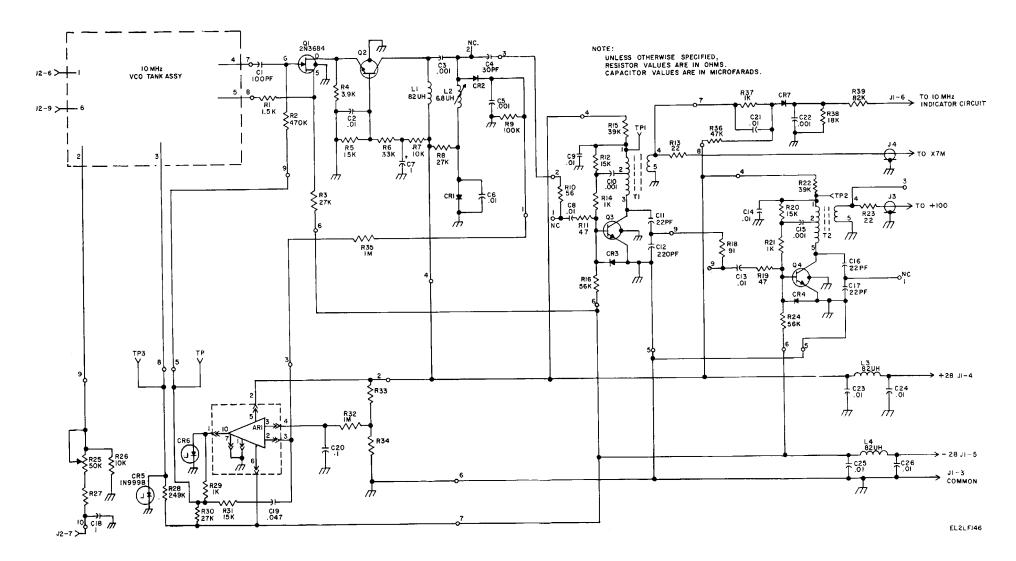

| 3-63                 | 10 MHz vco tank circuit 1A3A14A3, schematic diagram                             |              |

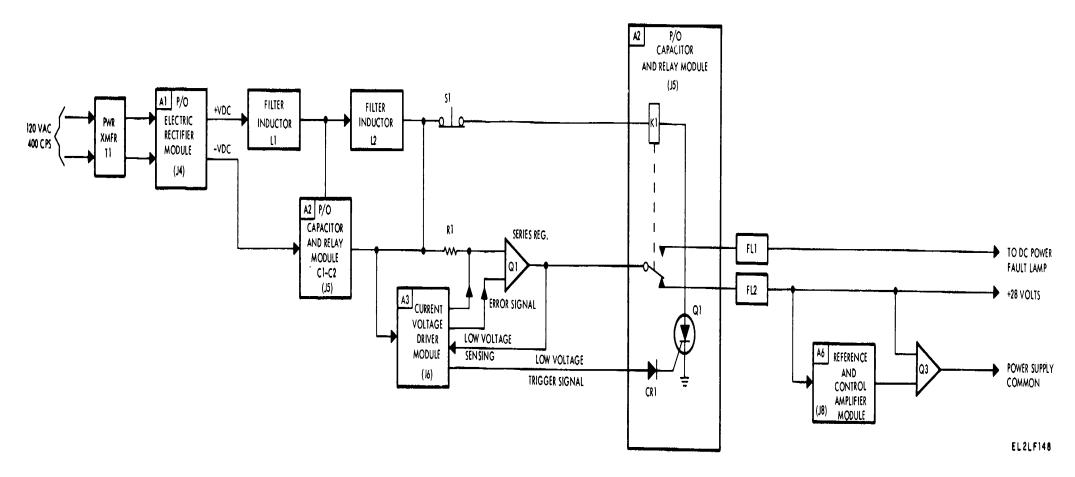

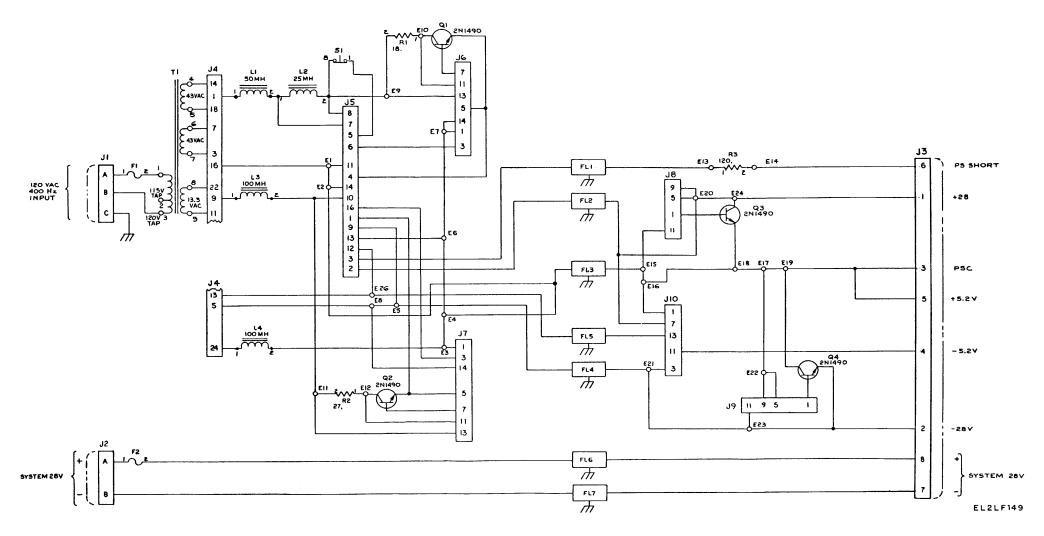

| 3-64                 | Electric rectifier, schematic diagram                                           |              |

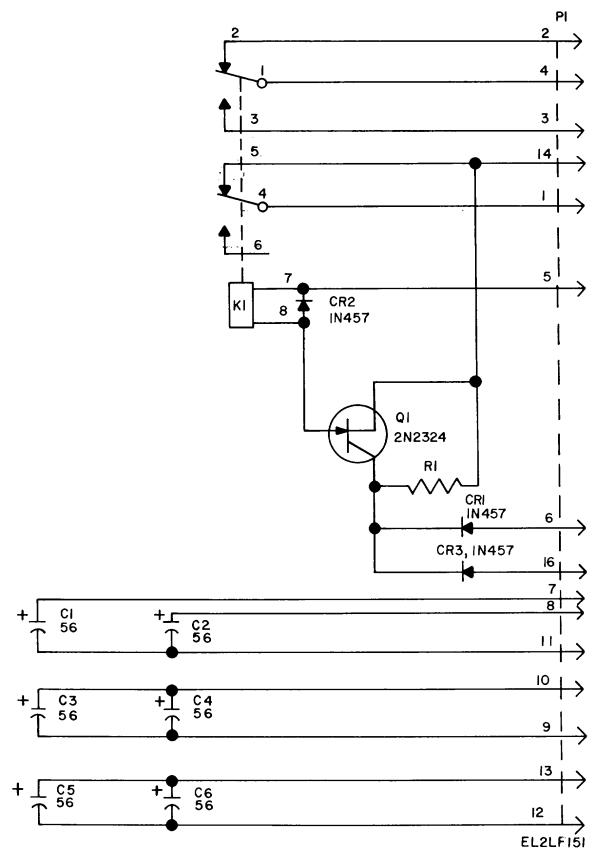

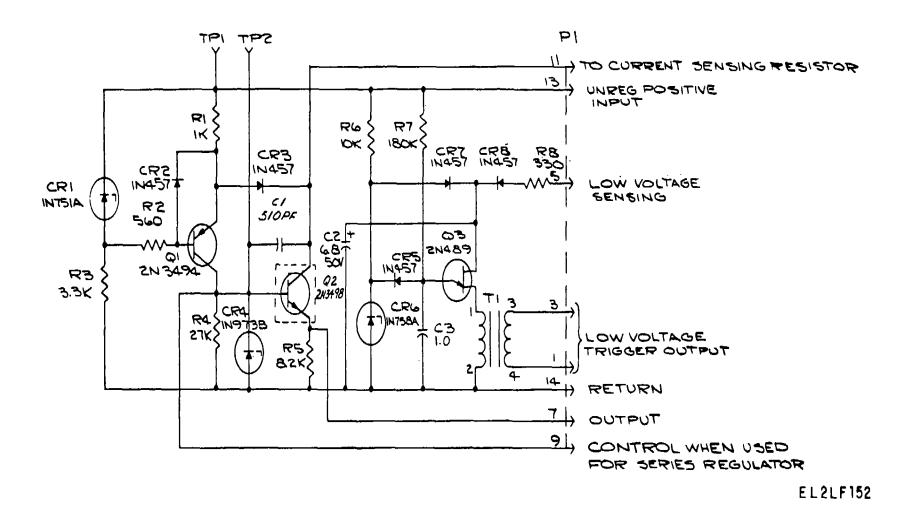

| 3-65                 | Capacitor and relay circuit board, schematic diagram                            |              |

| 3-66                 | Current and voltage drivers A3 and A4, schematic diagram                        |              |

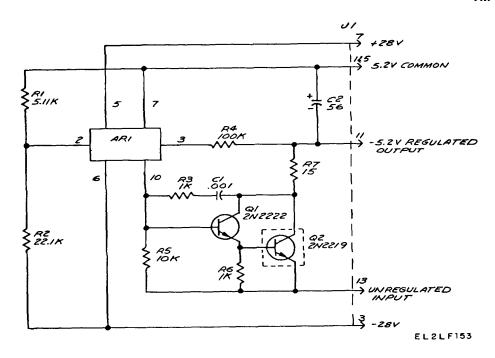

| 3-67                 | 5.2 volt regulator, schematic diagram                                           |              |

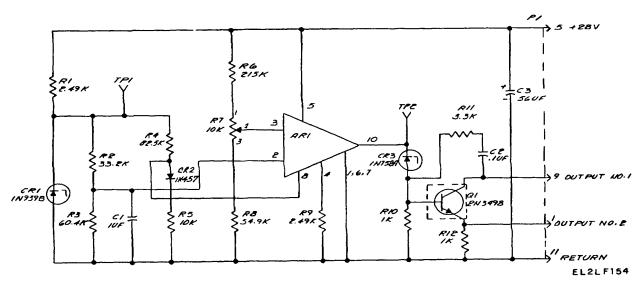

| 3-68                 | Reference and control amplifier, schematic diagram                              |              |

| 3-69                 | 70 MHz bandpass filter 1A3A14A5, schematic diagram                              |              |

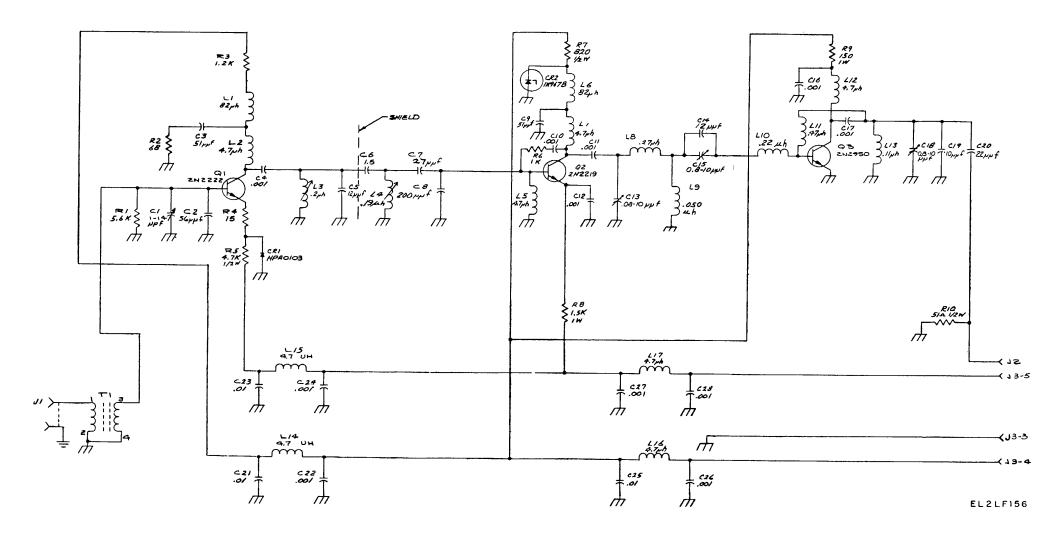

| 3-70                 | Divide by 100 countdown circuit A7, schematic diagram                           |              |

| 3-71                 | Integrated circuit device, typical logic diagram                                |              |

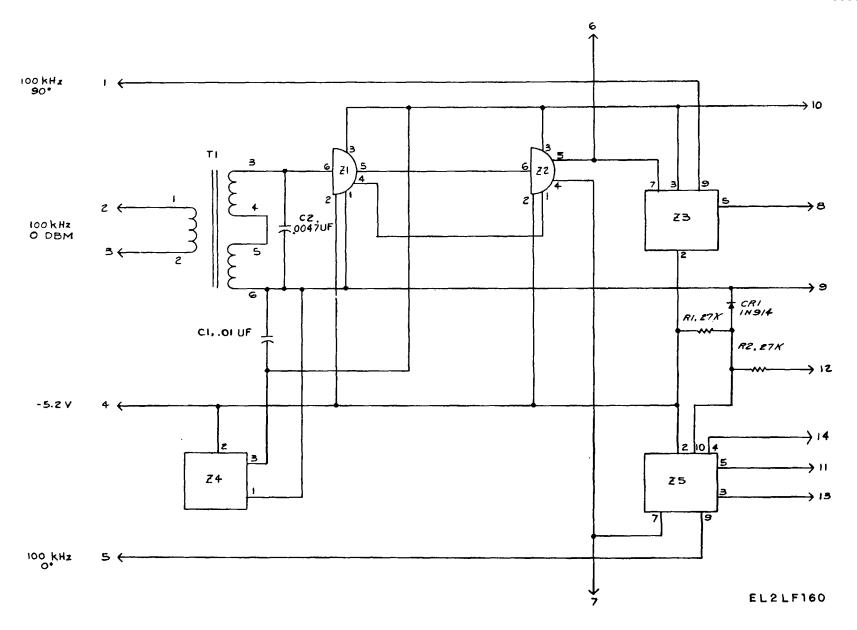

| 3-72                 | 100 kHz phase detector, schematic diagram                                       |              |

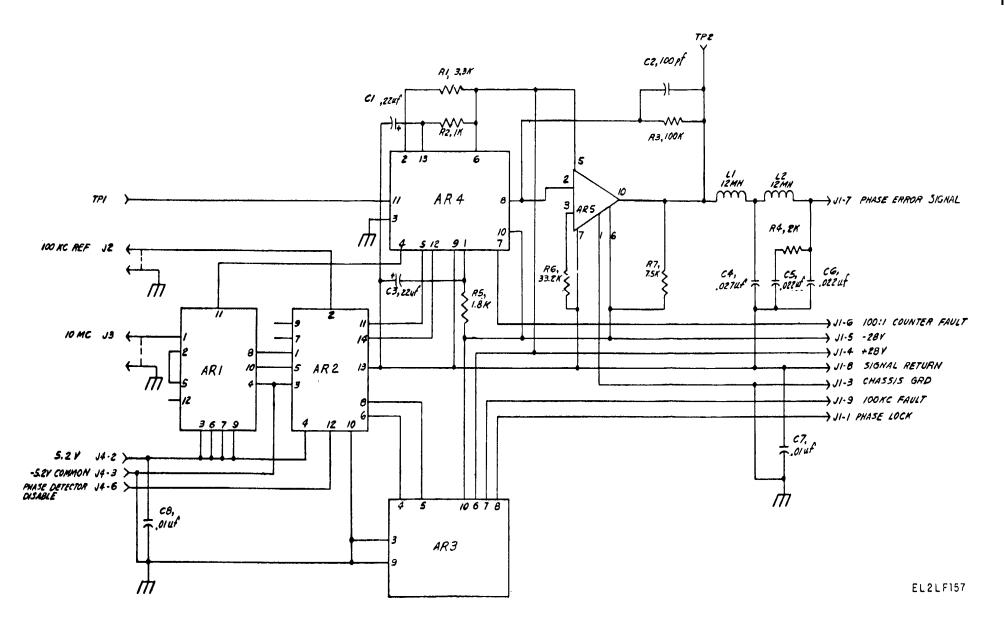

| 3-73                 | 100 kHz detector AR3, schematic diagram                                         |              |

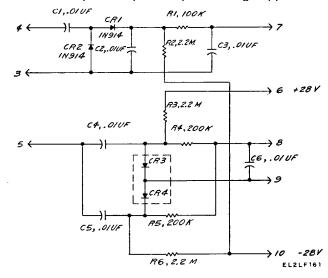

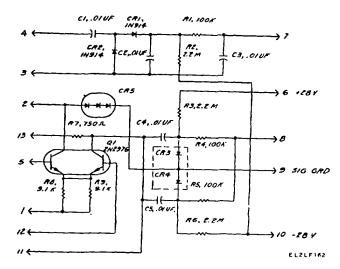

| 3-74                 | 100 kHz detector AR4, schematic diagram                                         | 3-88         |

| Figure                     | Litle                                                           | Page                    |

|----------------------------|-----------------------------------------------------------------|-------------------------|

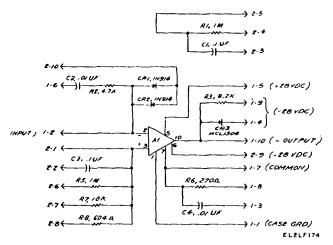

| 3-75                       | Phase lock loop amplifier 1A3A14A9, schematic diagram           | 3-89                    |

| 3-76                       | Baseband differential amplifier, schematic diagram              |                         |

| 3-77                       | Baseband operational amplifier, schematic diagram               |                         |

| 3-78                       | DC amplifier Al, schematic diagram                              |                         |

| 3-79                       | Meter compensation network, schematic diagram                   |                         |

| 3-80                       | Baseband preemphasis network A25, schematic diagram             |                         |

| 3-81                       | Baseband preemphasis network A32, schematic diagram             | 3-91                    |

| 3-82                       | Twin-tee network and level control circuit, schematic diagram   | 3-92                    |

| 3-83                       | Baseband preemphasis network A37, schematic diagram             |                         |

| 3-84                       | Preemphasis network N1, input and output characteristics        | 3-92                    |

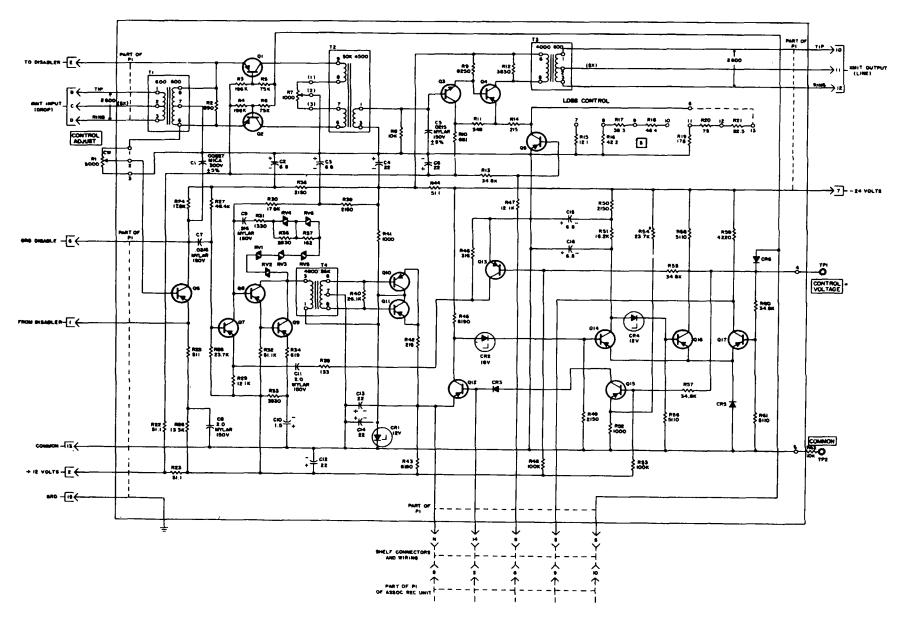

| 3-85                       | Echo suppressor transmitter, simplified schematic diagram       |                         |

| 3-86                       | Echo suppressor transmitter, schematic diagram                  |                         |

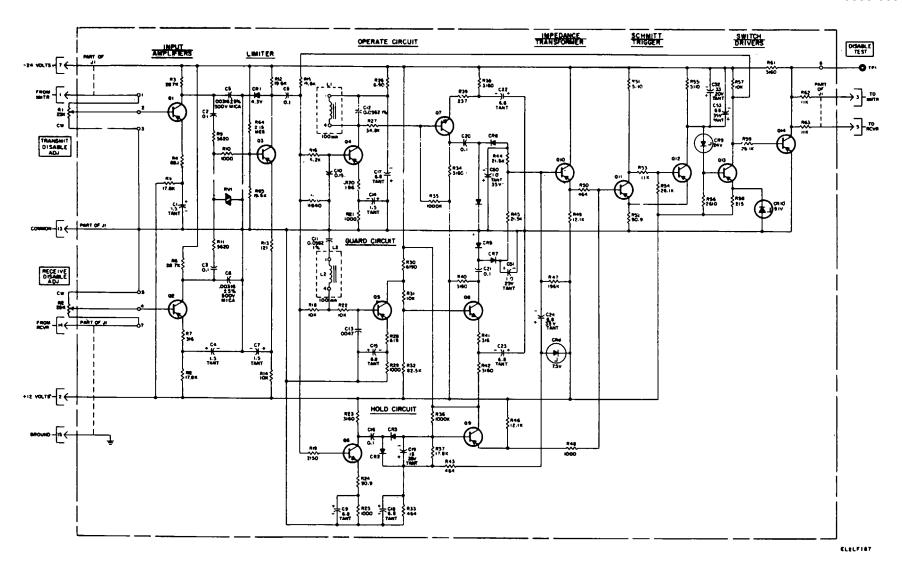

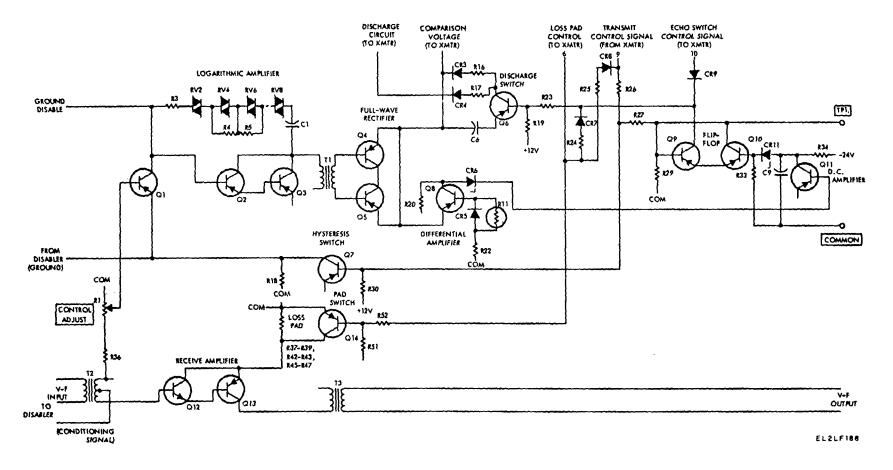

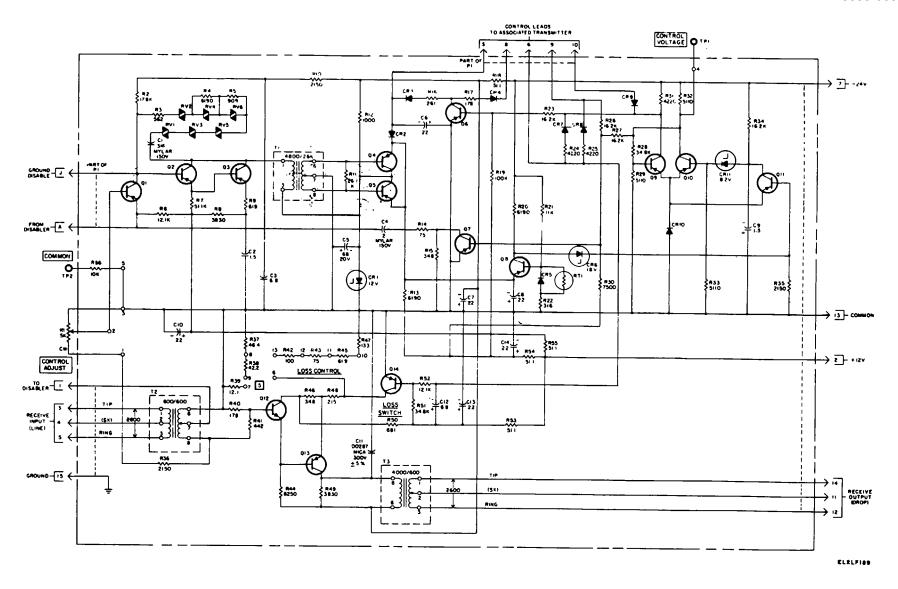

| 3-87                       | Echo suppressor disabler, schematic diagram                     |                         |

| 3-88                       | Echo suppressor receiver, simplified schematic diagram          |                         |

| 3-89                       | Echo suppressor receiver, schematic diagram                     |                         |

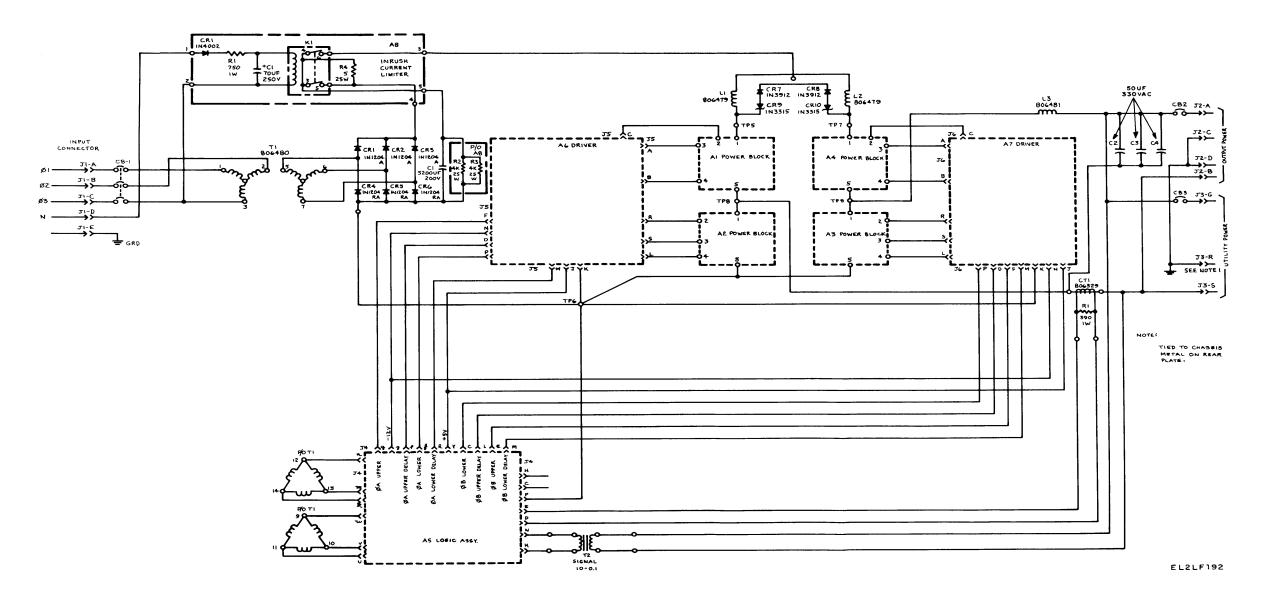

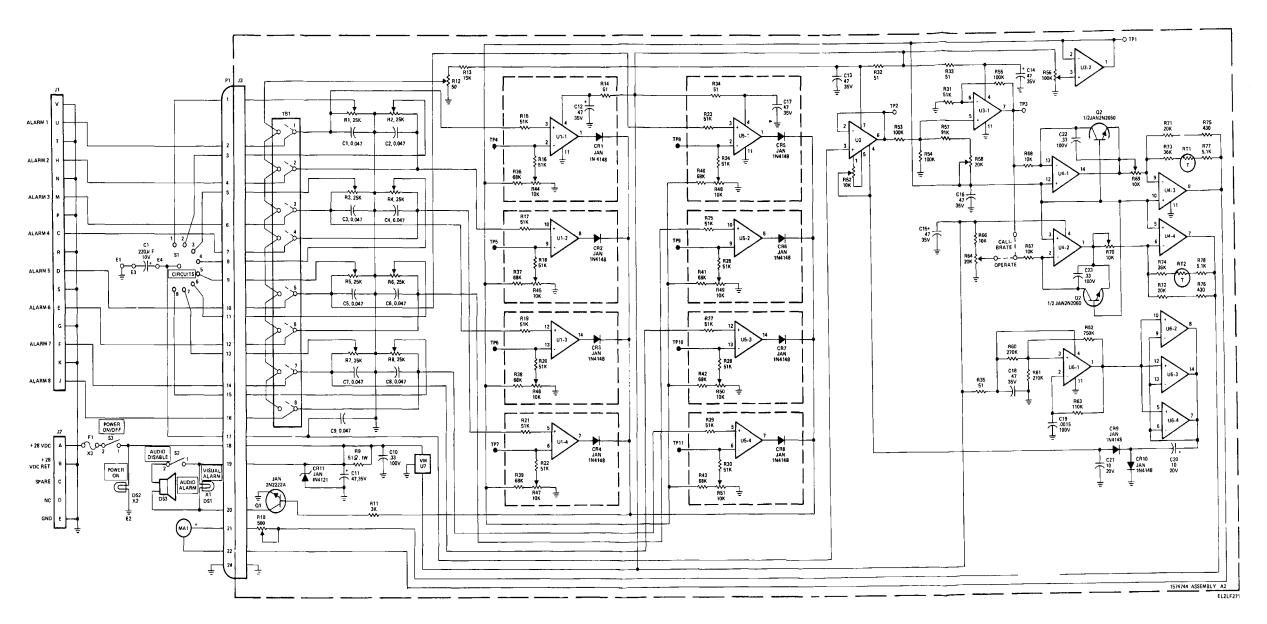

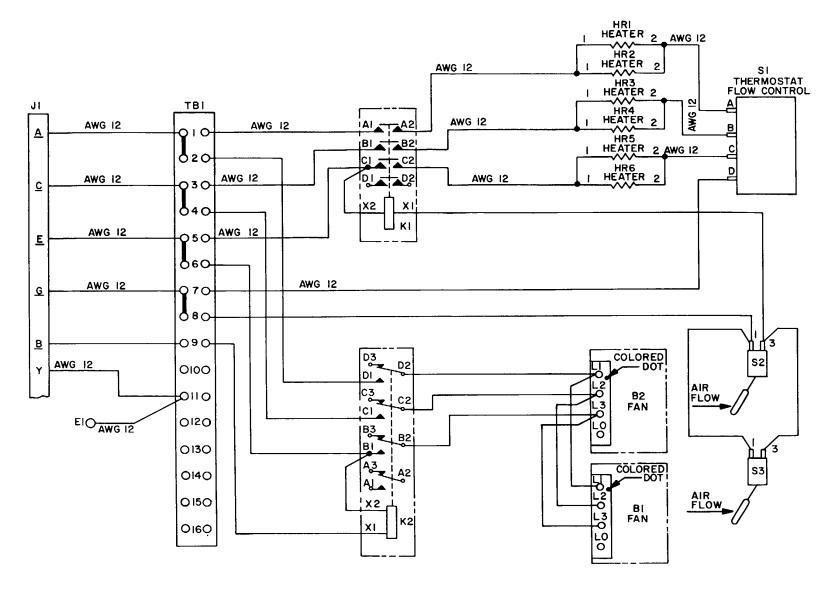

| 3-90                       | Fan control assembly 1A3A19, schematic diagram                  | 3-107                   |

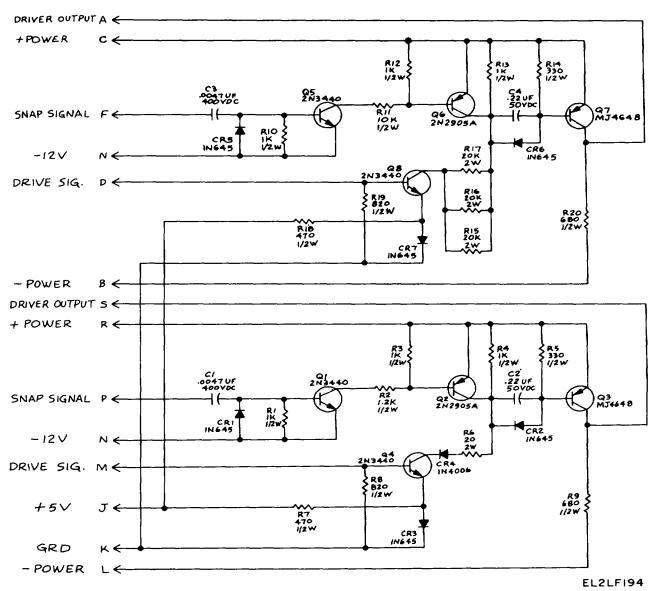

| 3-91                       | Driver amplifiers A6 and A7, schematic diagram                  | 3-108                   |

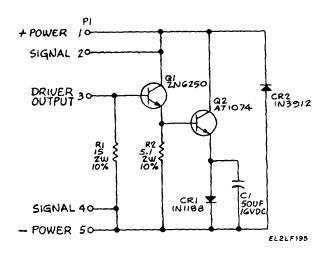

| 3-92                       | Power blocks A1, A2, A3, and A4, schematic diagram              | 3-109                   |

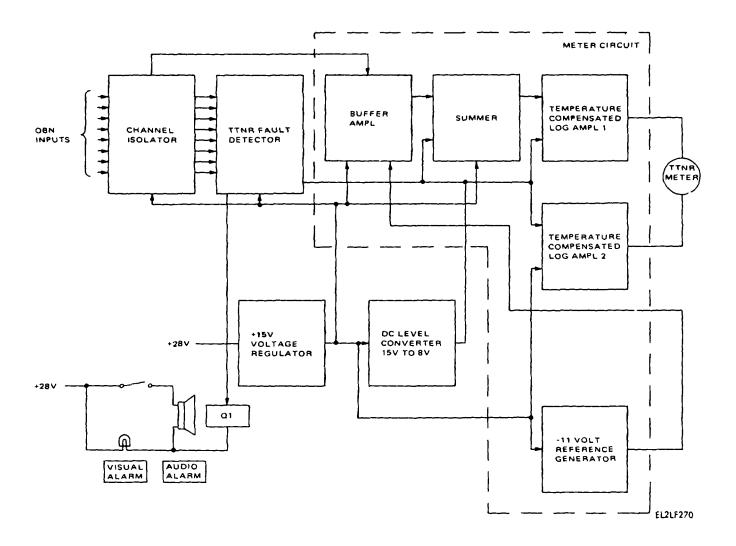

| 3-92.1                     | OBN monitor panel (1A3A24), block diagram                       | 3-110                   |

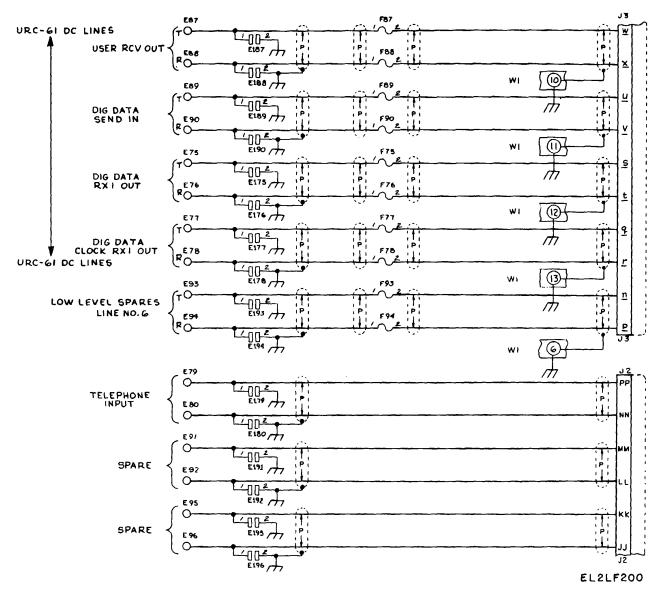

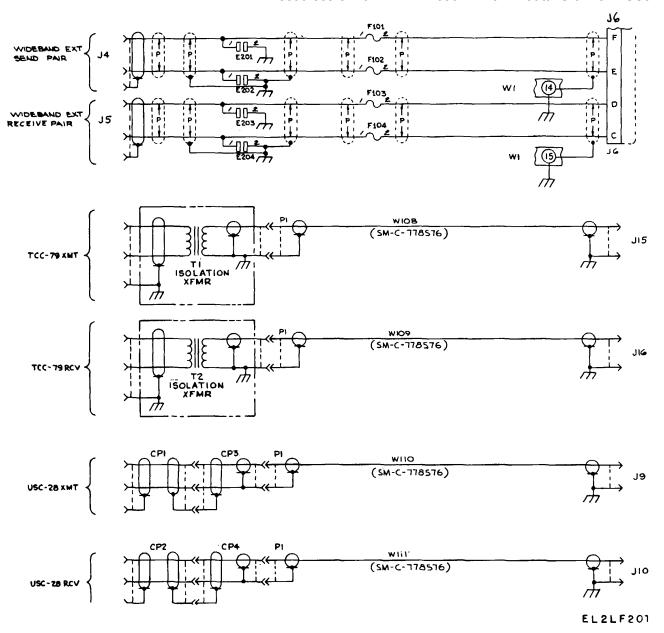

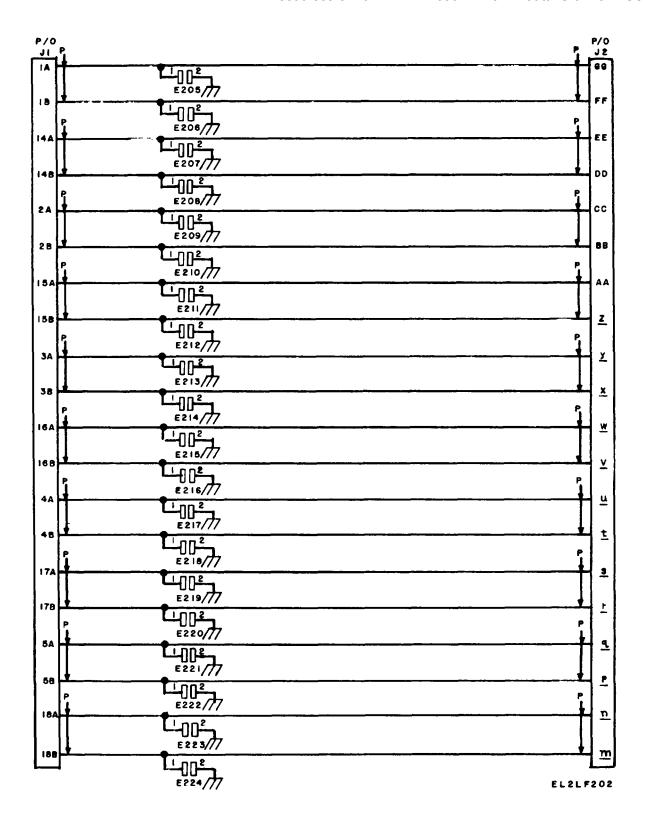

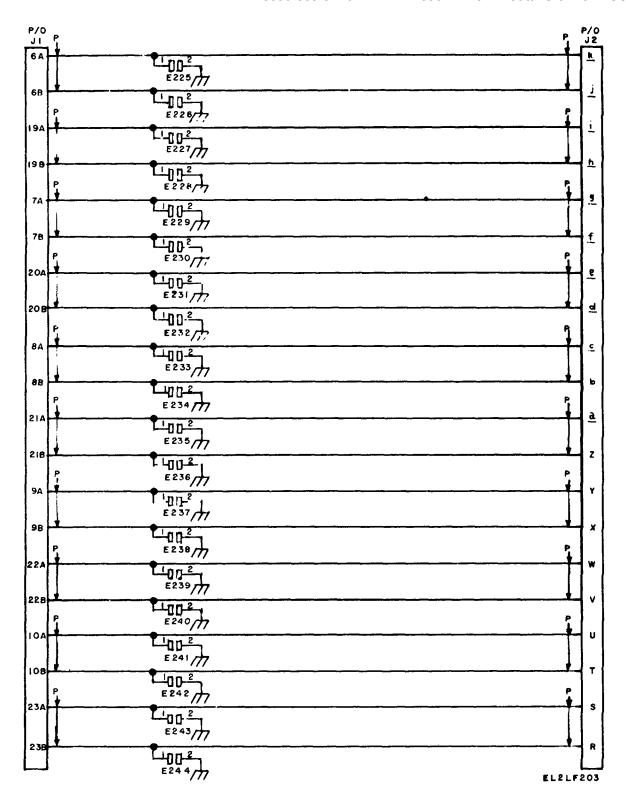

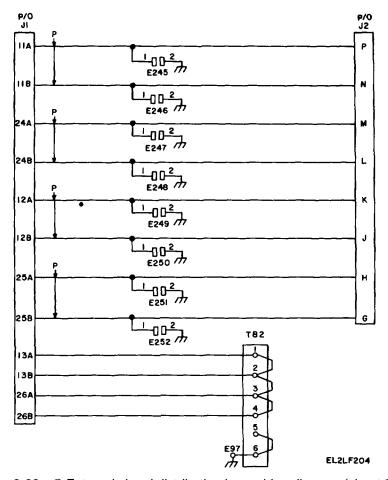

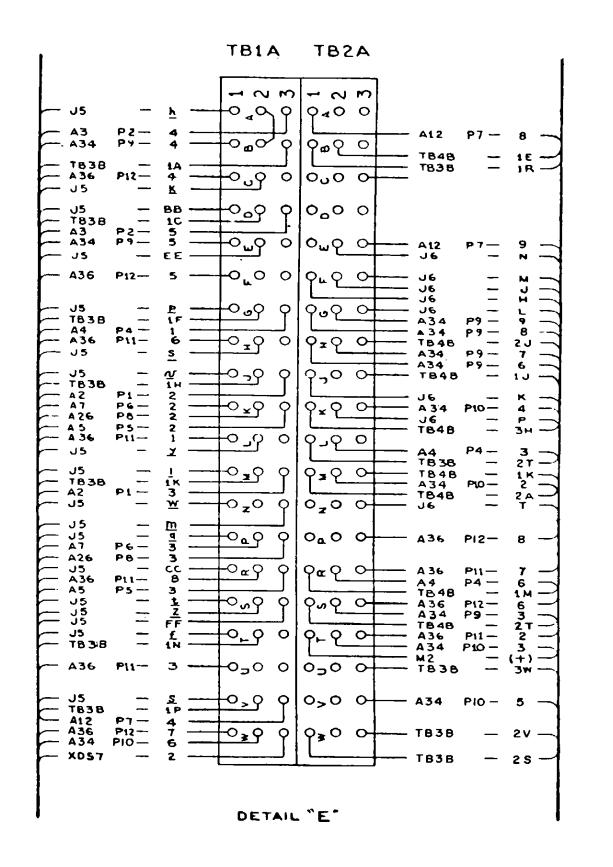

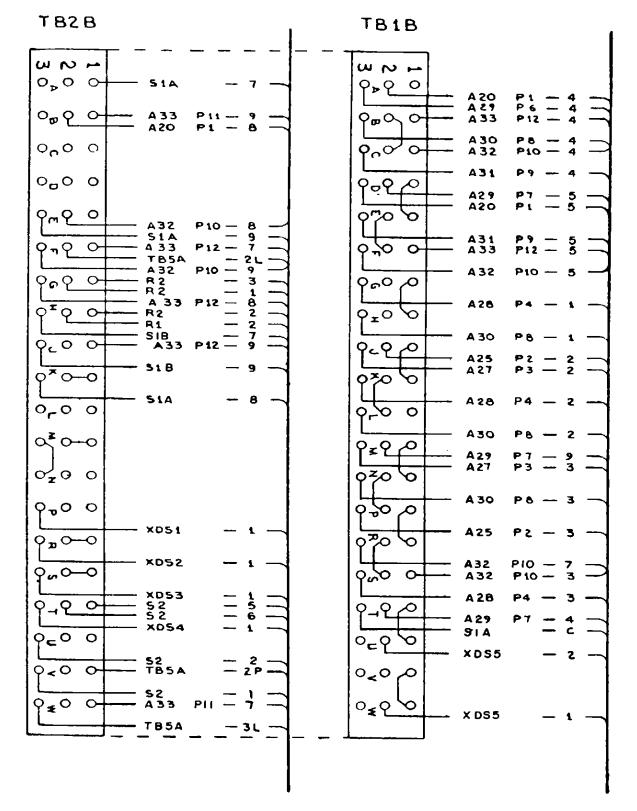

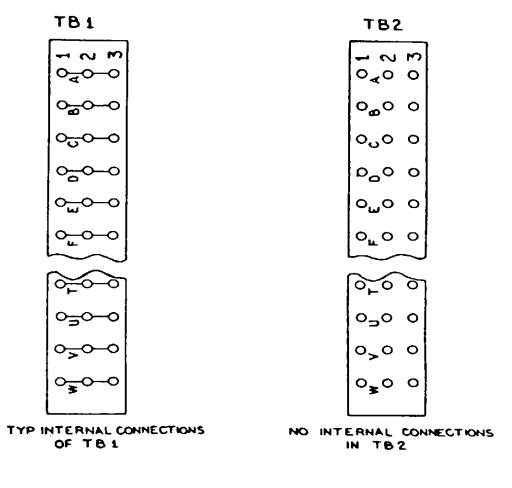

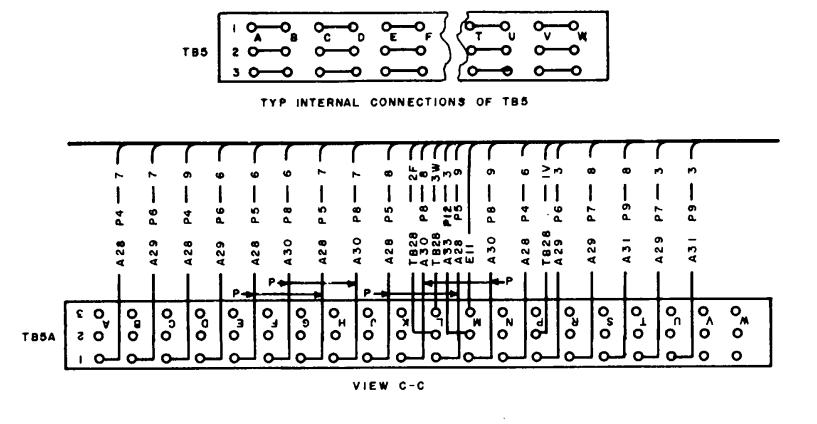

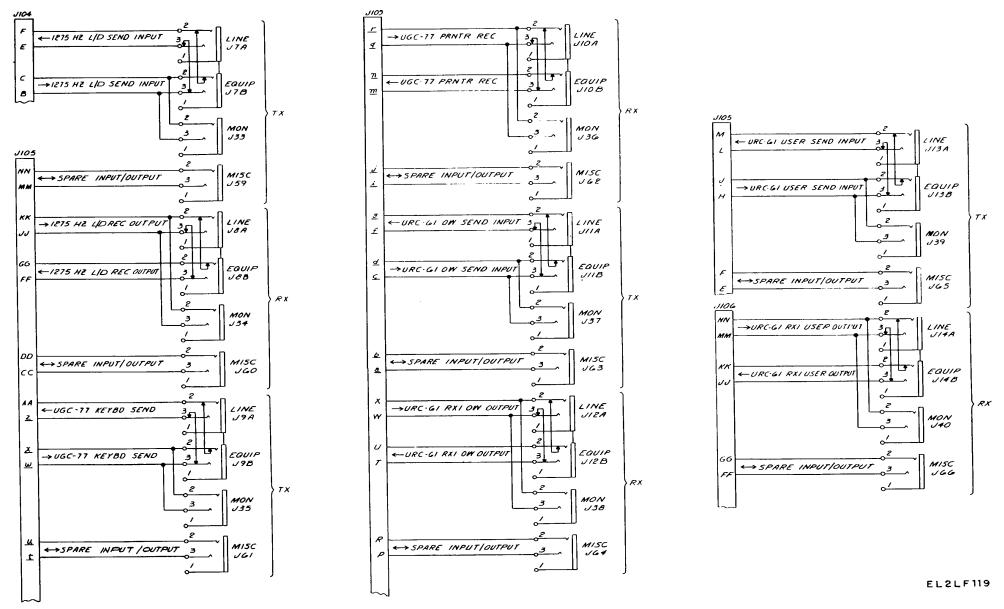

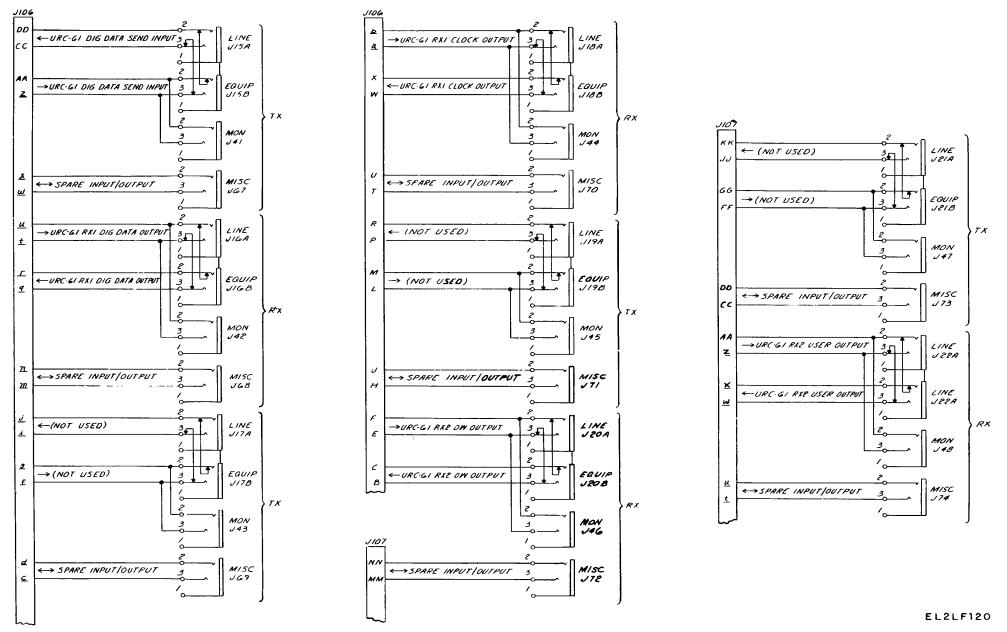

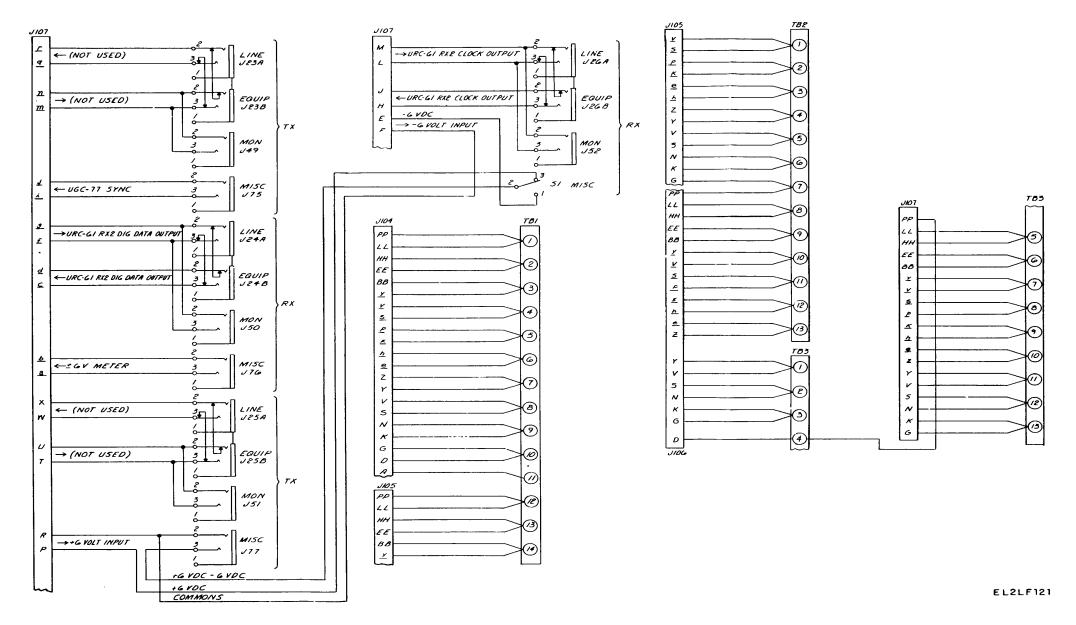

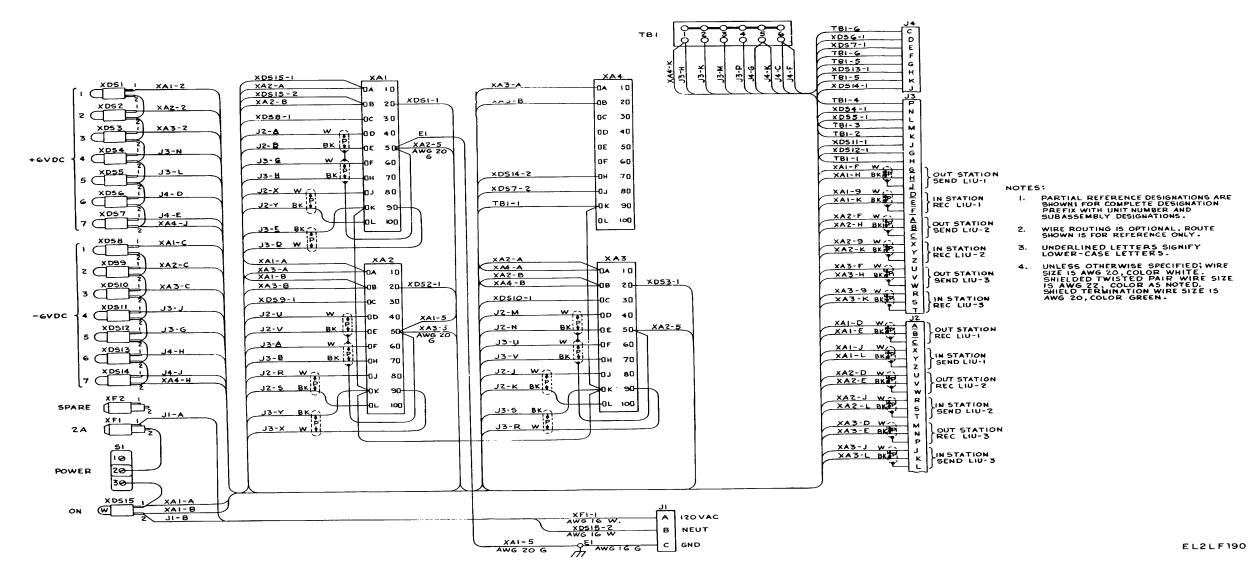

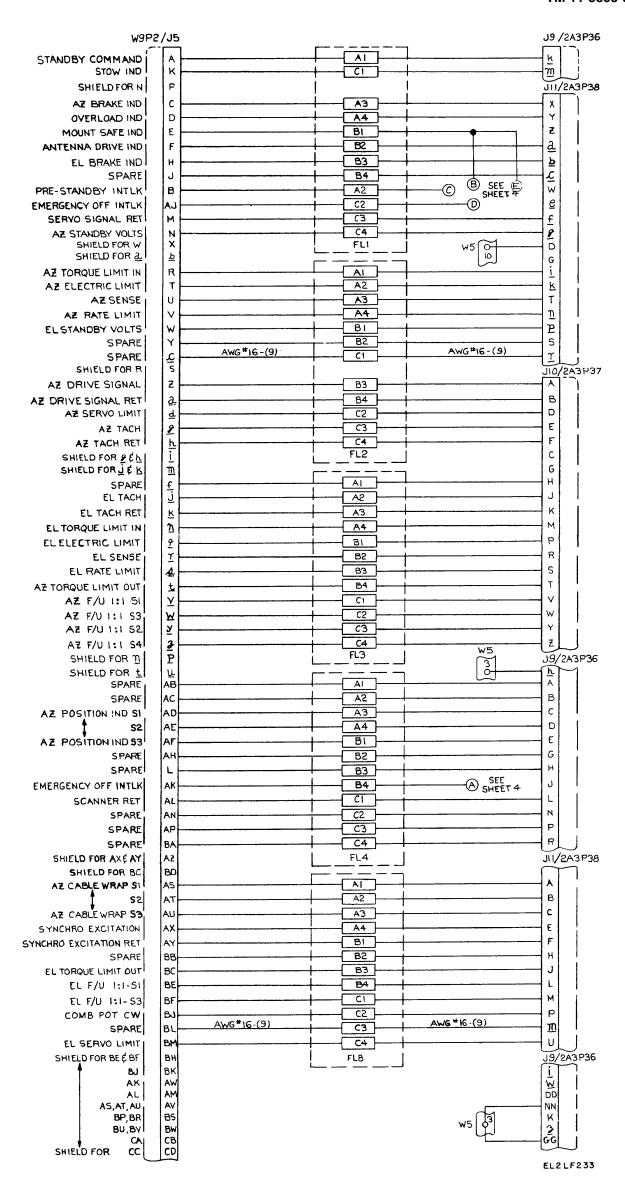

| 3-93①                      | External signal distribution box, wiring diagram (sheet 1 of 9) |                         |

| <b>3-93</b> ②              | External signal distribution box, wiring diagram (sheet 2 of 9) |                         |

| 3-93③                      | External signal distribution box, wiring diagram (sheet 3 of 9) |                         |

| 3-93④                      | External signal distribution box, wiring diagram (sheet 4 of 9) |                         |

| <b>3-93</b> ⑤              | External signal distribution box, wiring diagram (sheet 5 of 9) |                         |

| 3-93⑥                      | External signal distribution box, wiring diagram (sheet 6 of 9) |                         |

| 3-93⑦                      | External signal distribution box, wiring diagram (sheet 7 of 9) |                         |

| 3-93®                      | External signal distribution box, wiring diagram (sheet 8 of 9) |                         |

| 3-93⑨                      | External signal distribution box, wiring diagram (sheet 9 of 9) |                         |

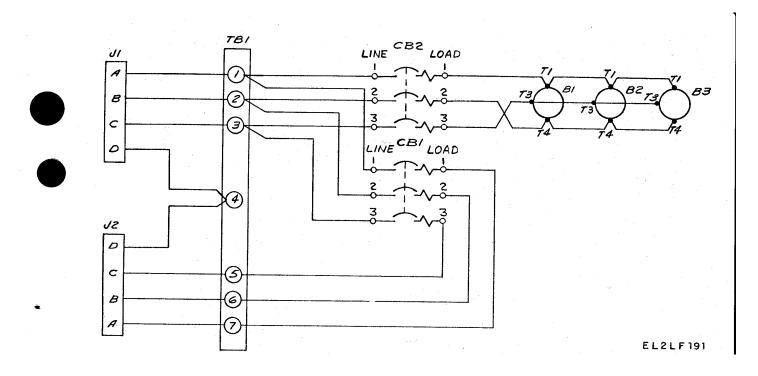

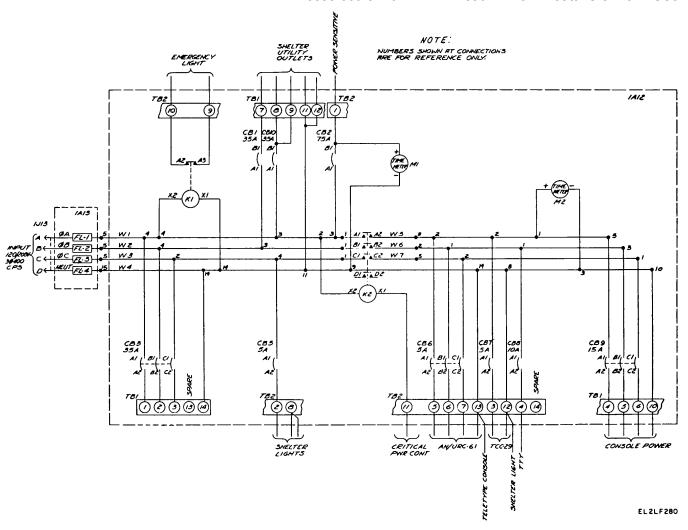

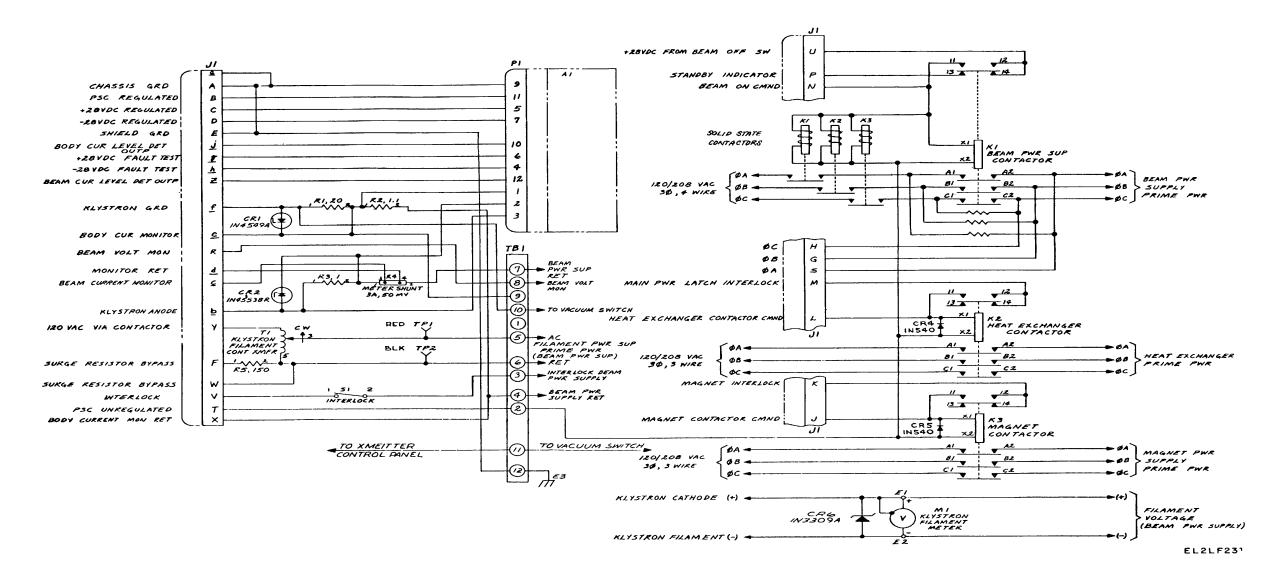

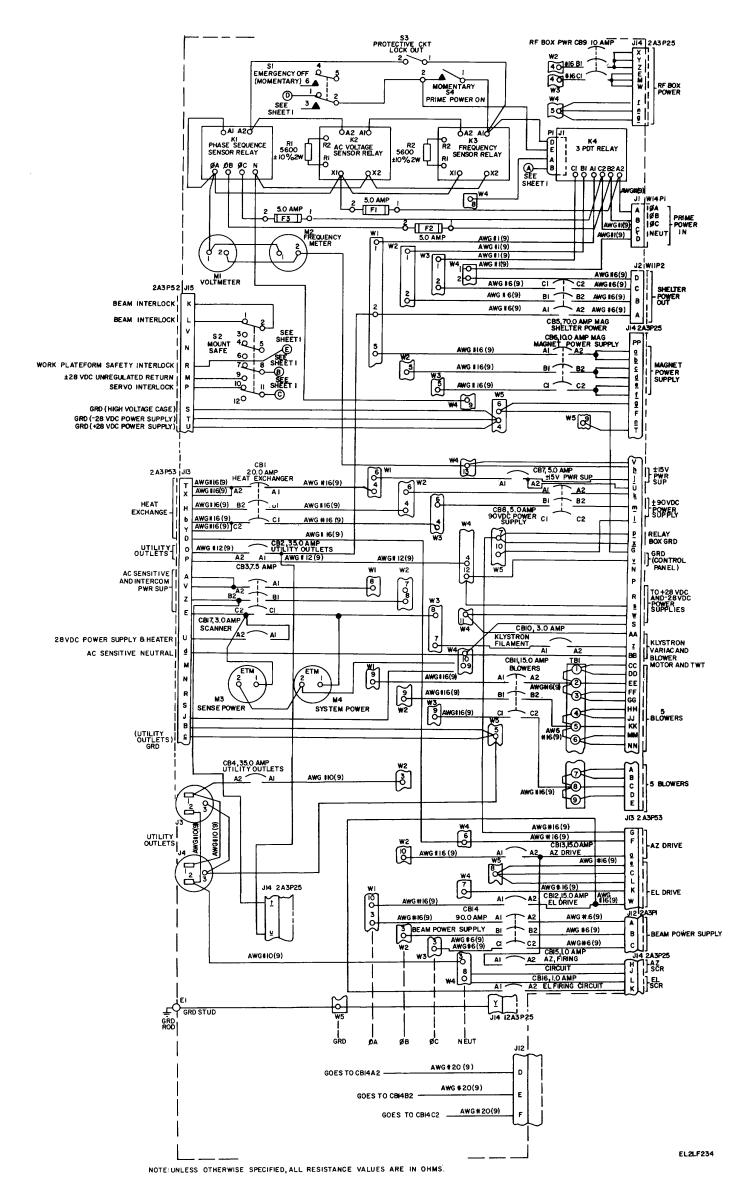

| 3-94                       | Primary power distribution assembly 1A12, schematic diagram     | 3-119                   |

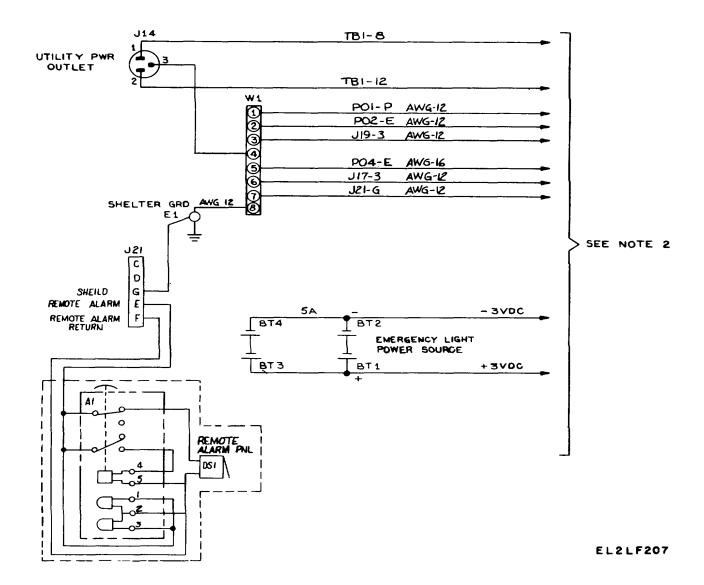

| 3-95                       | External dc power distribution box 1A14, schematic diagram      |                         |

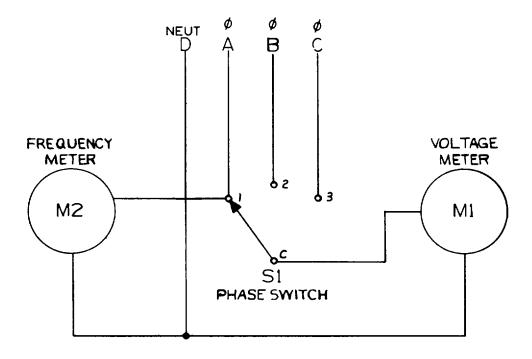

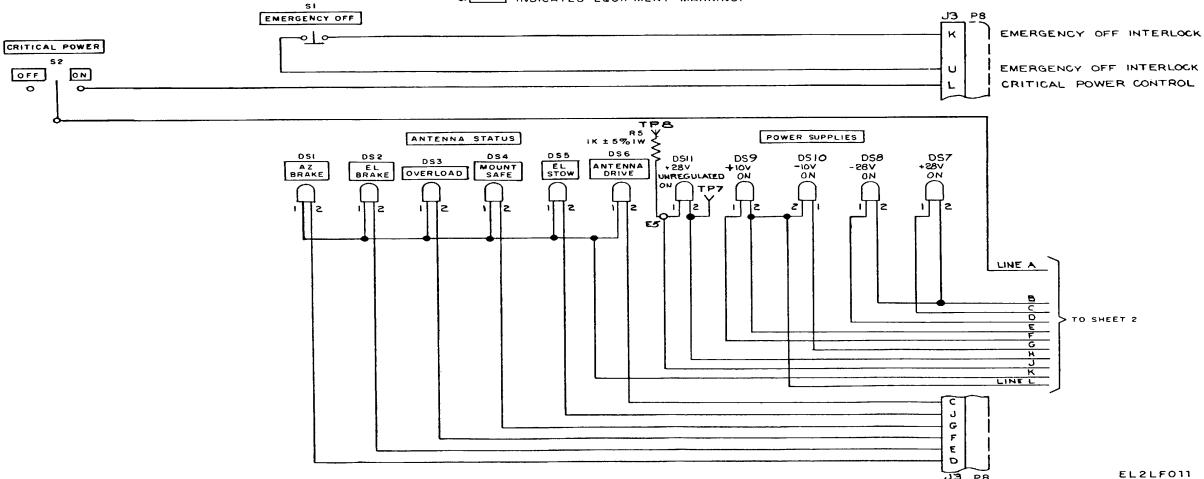

| 3-96                       | Primary power monitor panel 1A16, schematic diagram             | 3-121                   |

| 3-97                       | Power supply PS1, schematic diagram                             | 3-122                   |

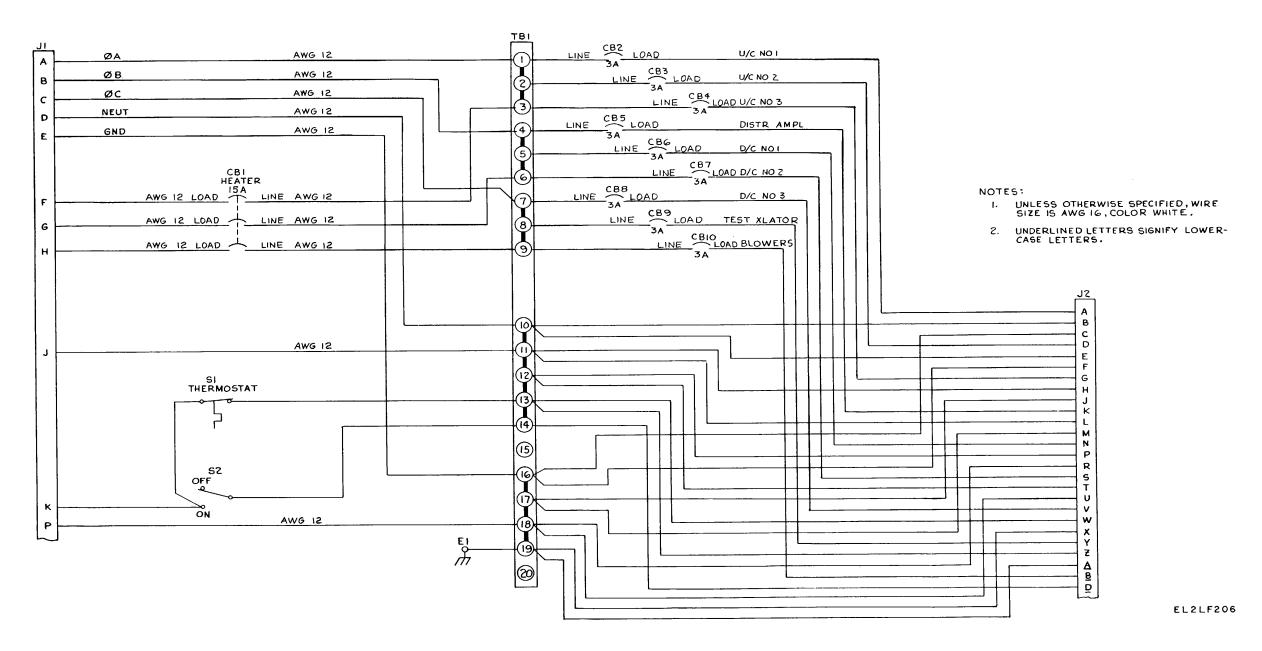

| 3-98                       | Heat transfer system, wiring diagram                            |                         |

| 3-99                       | Latch circuit No. 1, schematic diagram                          |                         |

| 3-100                      | Latch circuit No. 4, schematic diagram                          |                         |

| 3-101                      | Latch circuit No. 2, schematic diagram                          |                         |

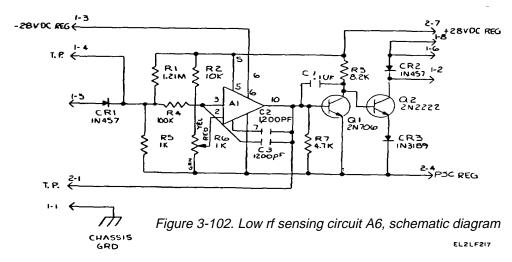

| 3-102                      | Low rf sensing circuit A6, schematic diagram                    | 3-127                   |

| 3-103                      | Latch circuit No. 3, schematic diagram                          |                         |

| 3-104                      | Isolator are sensing circuit, schematic diagram                 |                         |

| 3-105                      | Diode switch trigger circuit A9, schematic diagram              |                         |

| 3-106                      | Detector amplifier, schematic diagram                           |                         |

| 3-107                      | Arc detector amplifier A13, schematic diagram                   |                         |

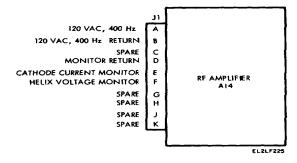

| 3-108                      | RF amplifier A14 input and output characteristics               |                         |

| 3-109                      | RF amplifier A15, schematic diagram                             |                         |

| 3-110                      | RF amplifier A15, wiring diagram                                |                         |

| 3-111                      | DC amplifier AR1, input and output characteristics              |                         |

| 3-112                      | Comparator amplifier AR2, input and output characteristics      |                         |

| 3-113                      | RF head, schematic diagram                                      | 3-136                   |

| 3-114                      | High voltage cage 2A3All component board, schematic diagram     |                         |

| 3-115                      | Phase sensing relay Ki, signal characteristics                  |                         |

| 3-116                      | AC voltage sensing relay K2, signal characteristics             |                         |

| 3-117                      | Frequency sensing relay K3, signal characteristics              |                         |

| 3-118                      | Primary power contactor K4, schematic diagram                   | 2 120                   |

| 3-119<br>3-120             | Solid state contactor, schematic diagram                        |                         |

| 3-120<br>3-121             | Servo amplifier A17/A18, schematic diagram                      |                         |

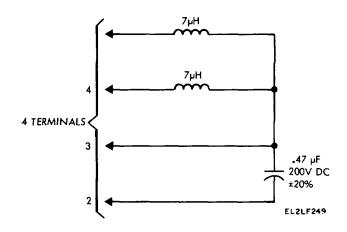

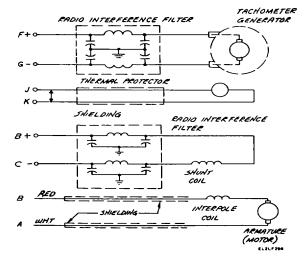

| 3-121<br>3-122             | RF filter, schematic diagram                                    |                         |

| 3-122<br>3-123             | Differential amplifier integrated circuit, schematic diagram    |                         |

| 3-123<br>3-124             | DTL NAND gate integrated circuit, schematic diagram             |                         |

| 3-12 <del>4</del><br>3-125 | Crossfire protection circuit 2A3A18A1A3, schematic diagram      |                         |

| 3-125<br>3-126             | Ser dv/dt filter 2A3A18AIA5, schematic diagram                  |                         |

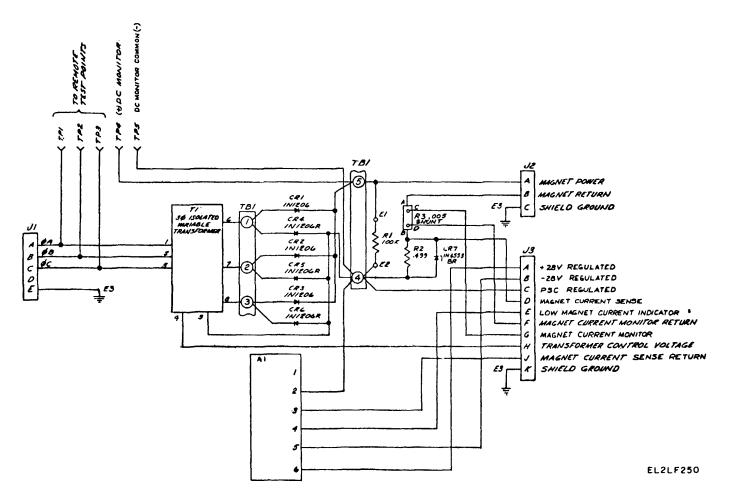

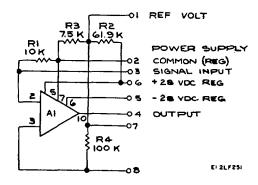

| 3-120<br>3-127             | Magnet power supply A21, schematic diagram                      |                         |

| 3-12 <i>1</i><br>3-128     | Magnet power supply component board, schematic diagram          |                         |

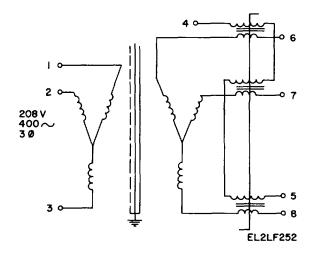

| 3-120<br>3-129             | Variable power transformer T1, schematic diagram                | 3-145<br>3 <b>-</b> 145 |

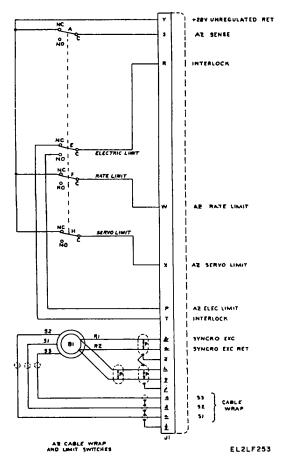

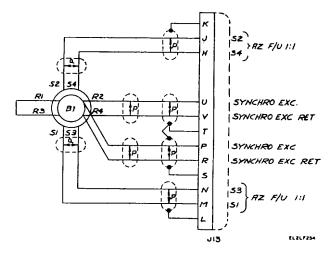

| 3-129<br>3-130             | Azimuth synchro and limit switch assembly, schematic diagram    |                         |

| 3-130<br>3-131             | Azimuth resolver and gear box assembly, schematic diagram       |                         |

| Figure                 | Title                                                                                              | R3-213034-22-2<br>Page |

|------------------------|----------------------------------------------------------------------------------------------------|------------------------|

| -                      |                                                                                                    | J                      |

| 3-132                  | Azimuth synchro and gear box assembly, schematic diagram                                           | . 3-146                |

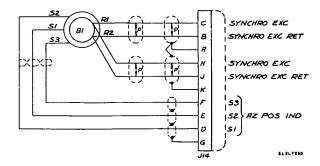

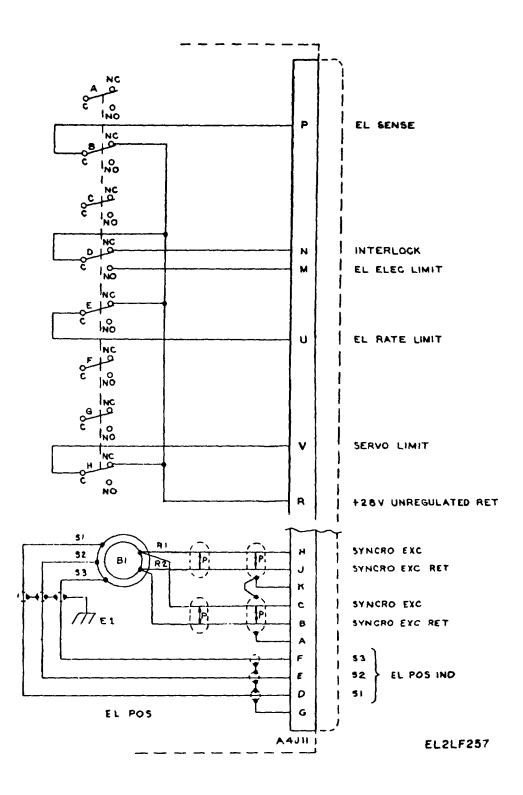

| 3-133<br>3-134         | Drive motor B1, schematic diagram  Elevation synchro and limit switch assembly schematic diagram   | 3-146                  |

| 3-134                  | Elevation resolver and gear box assembly, schematic diagram                                        | . 3-141<br>3-118       |

| 3-136                  | Azimuth/elevation scanner assembly, schematic diagram                                              |                        |

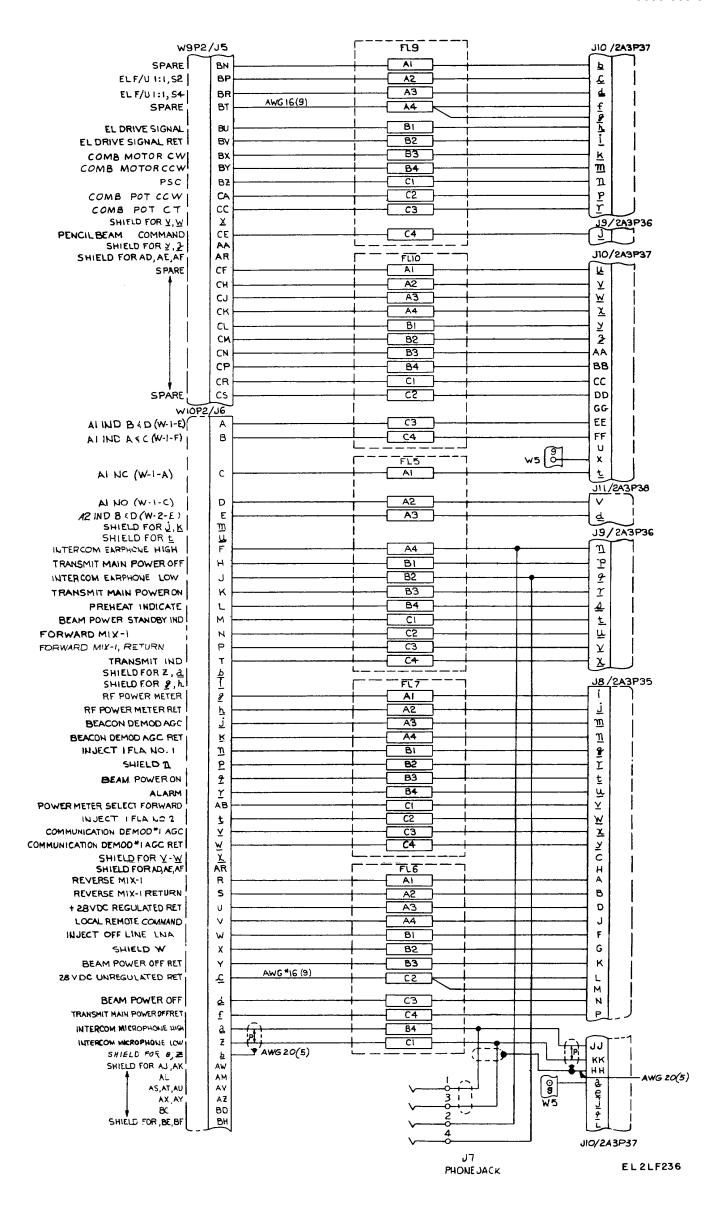

| 3-137 <sup>①</sup>     | Azimuth/elevation scanner assembly, wiring diagram (sheet 1 of 2)                                  | . 3-150                |

| 3-137@                 | Azimuth/elevation scanner assembly, wiring diagram (sheet 2 of 2)                                  | . 3-151                |

| FO 3-1                 | Distribution amplifier connection diagram                                                          | Back of manual         |

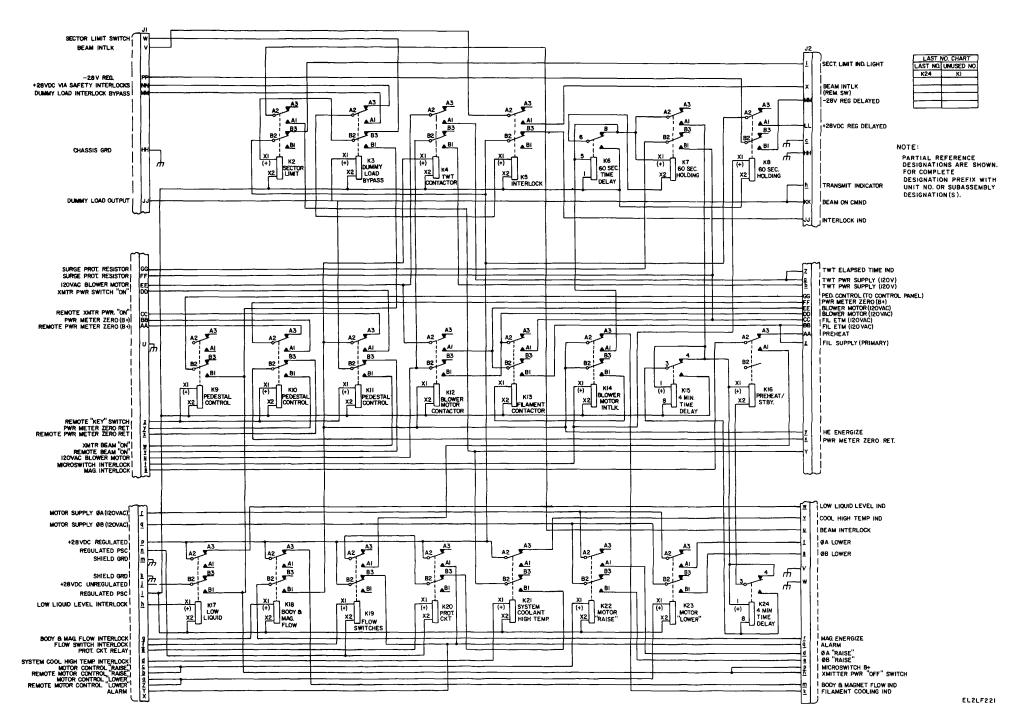

| FO 3-20                | Power distribution panel, schematic diagram (1 of 2)                                               |                        |

| FO 3-2②<br>FO 3-3      | Power distribution panel, schematic diagram (2 of 2)                                               |                        |

| FO 3-3<br>FO 3-4       | +28 vdc power supply PS5, schematic diagram                                                        |                        |

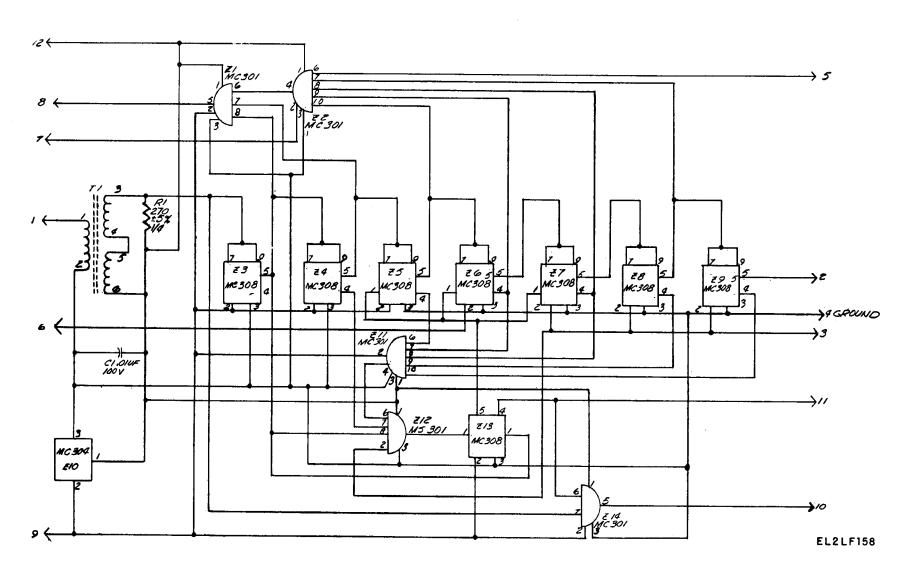

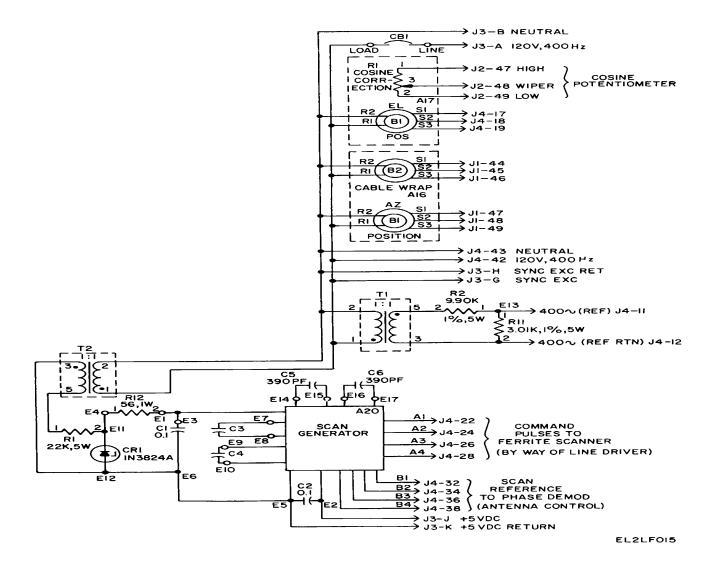

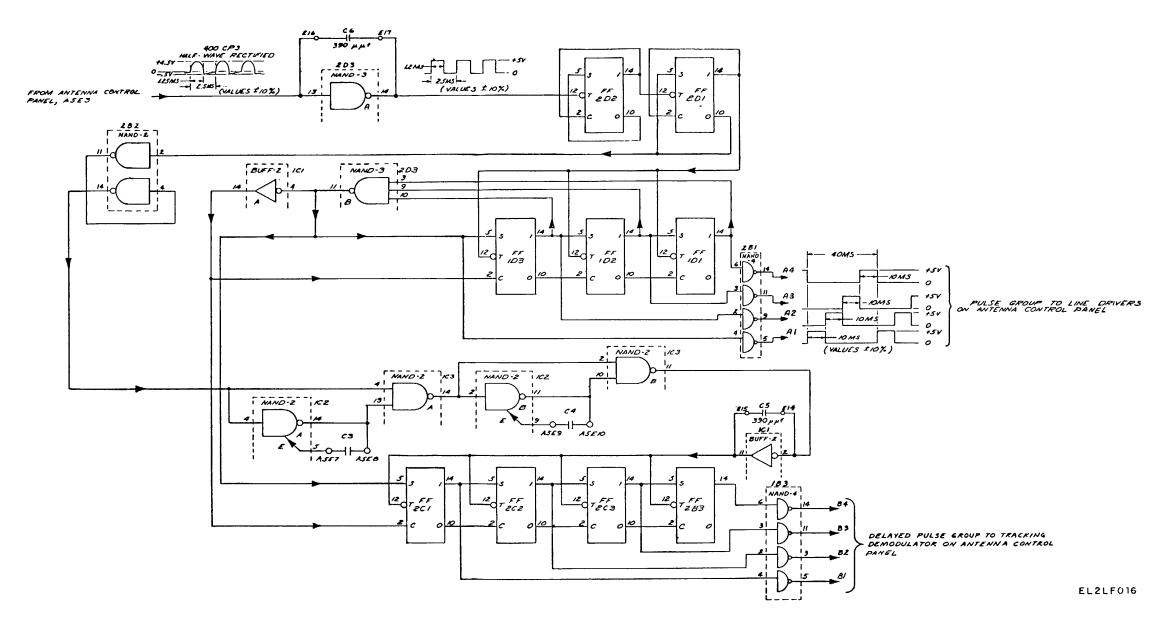

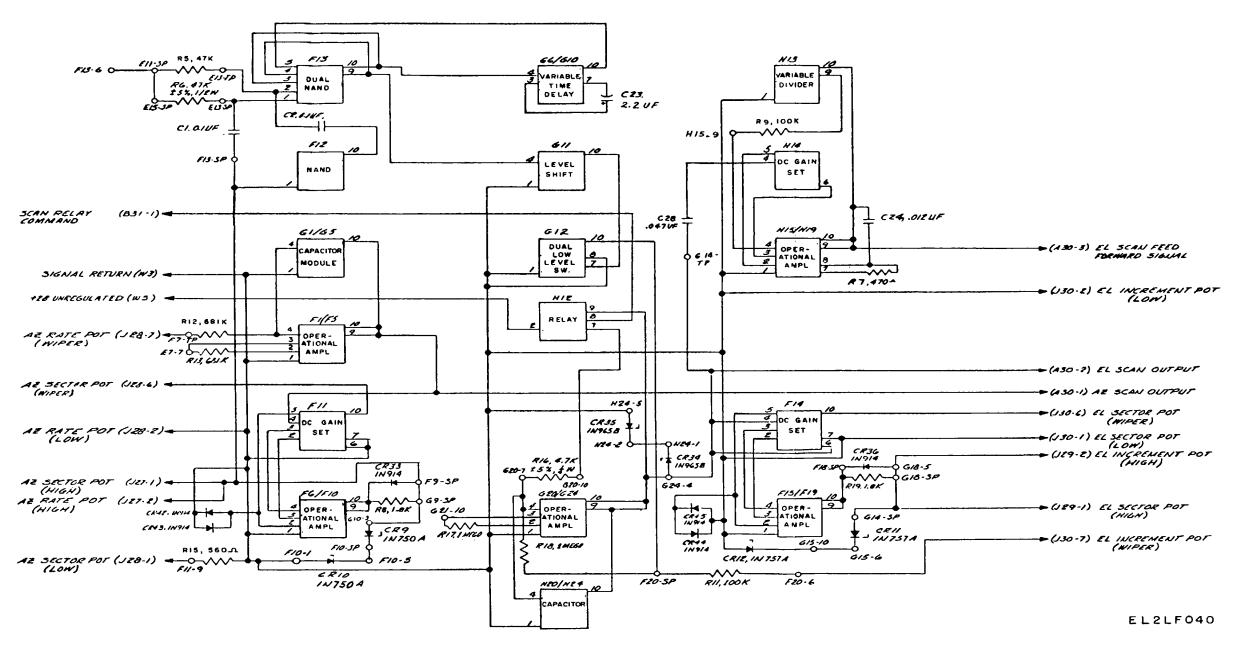

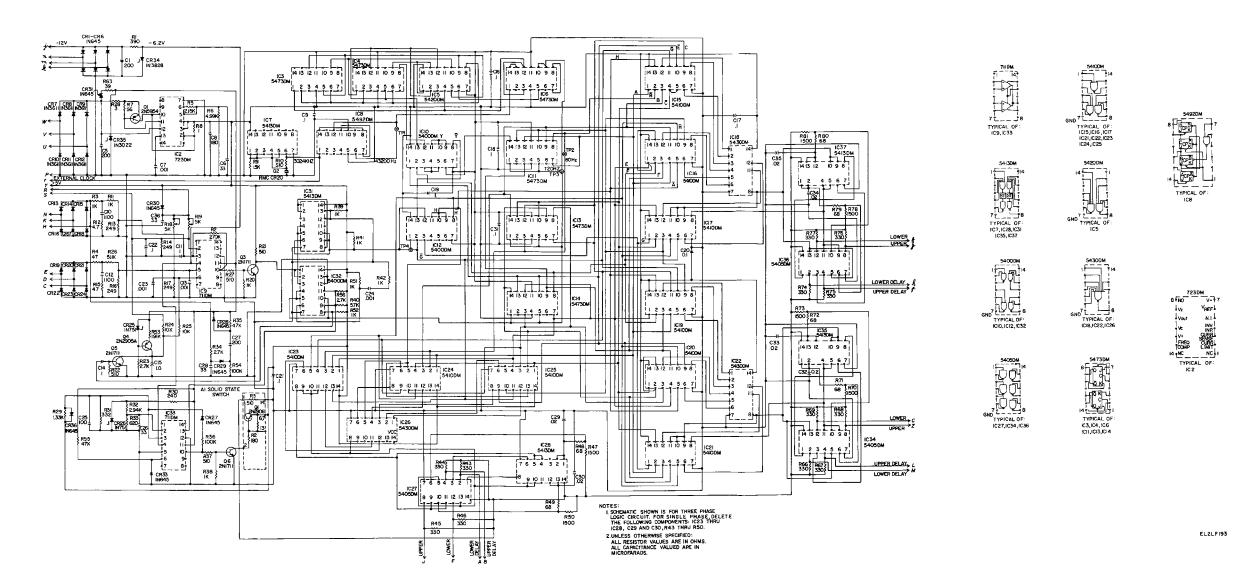

| FO 3-5                 | Scan generator A20, logic diagram                                                                  |                        |

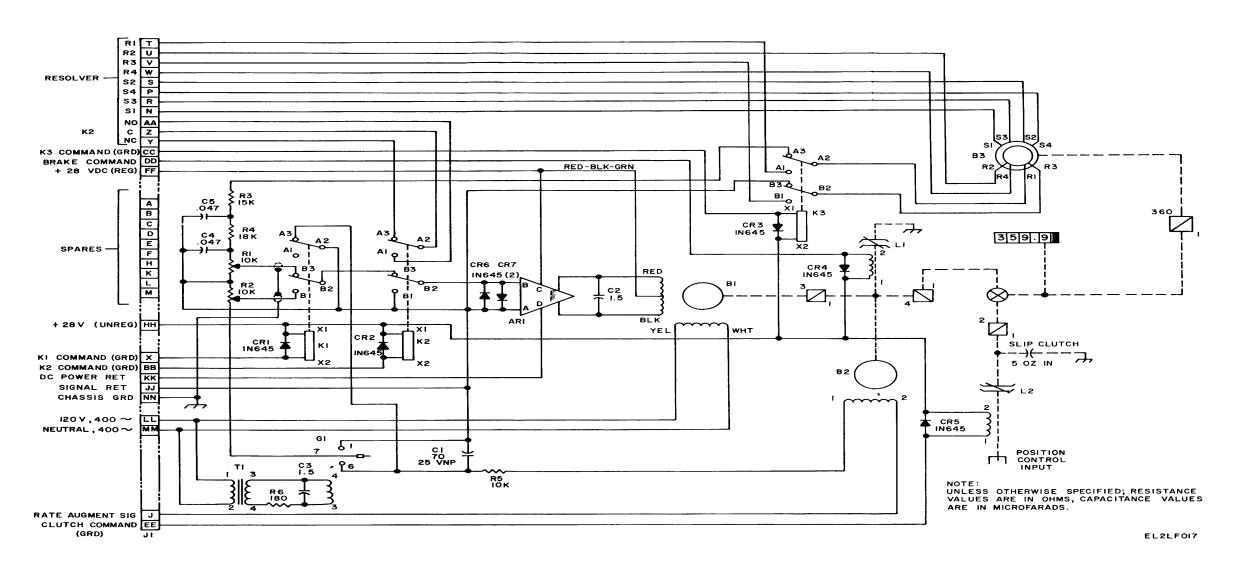

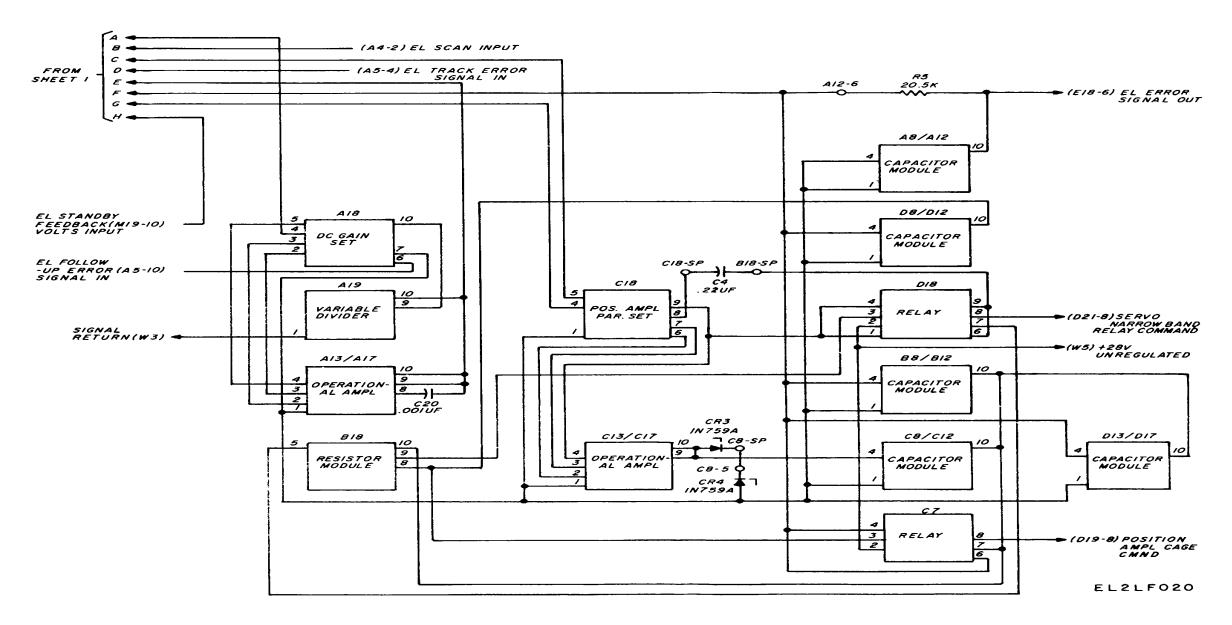

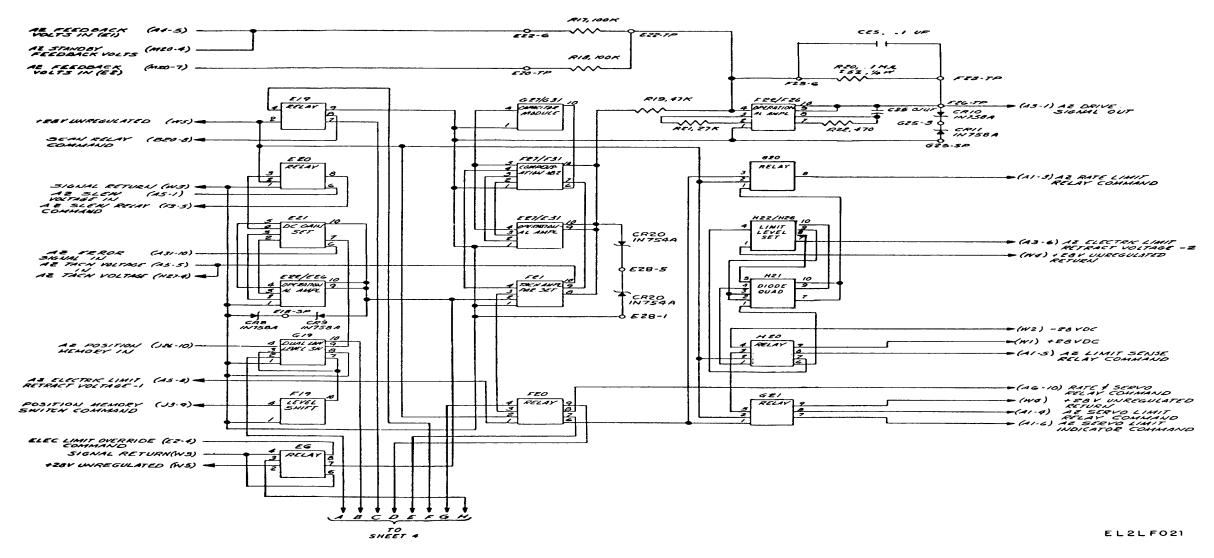

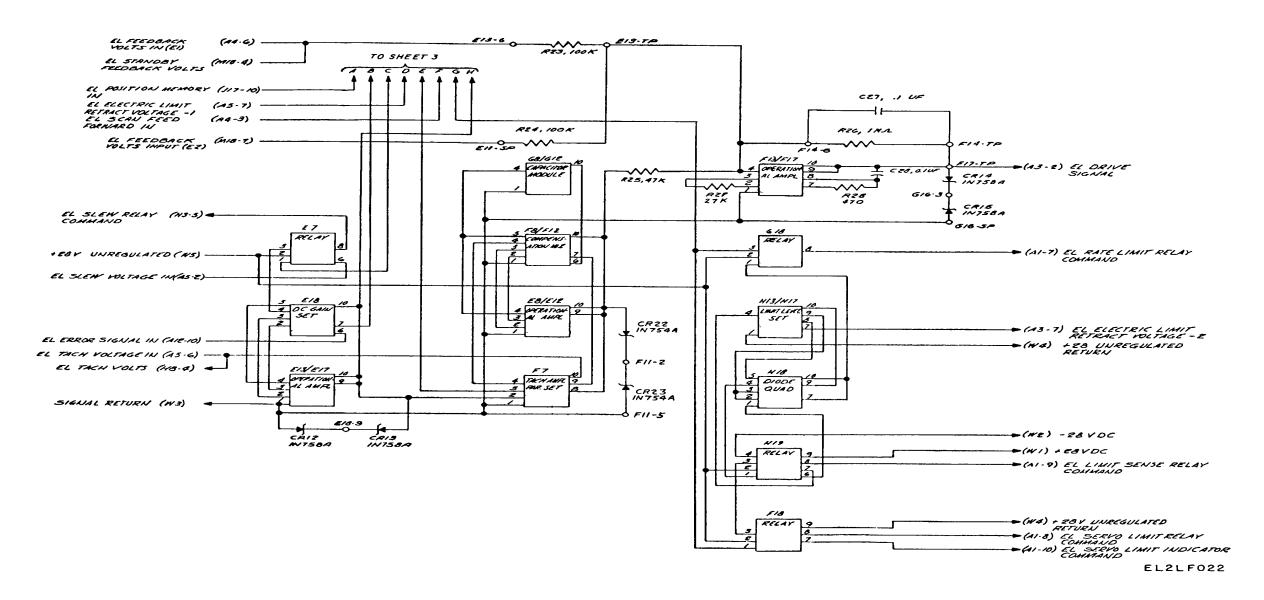

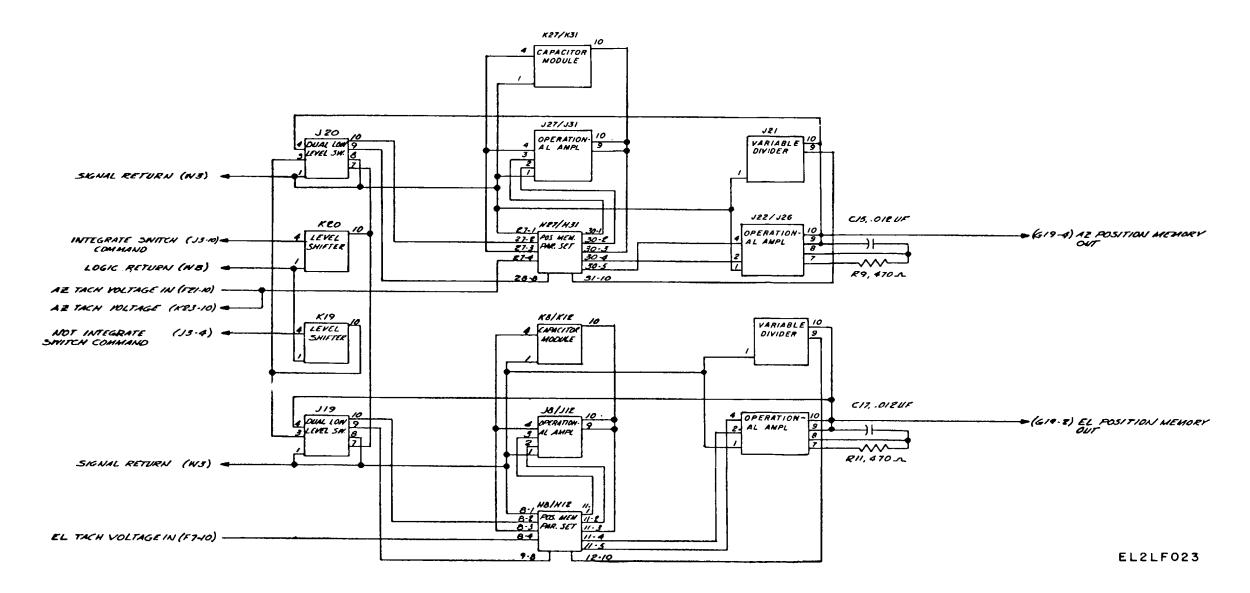

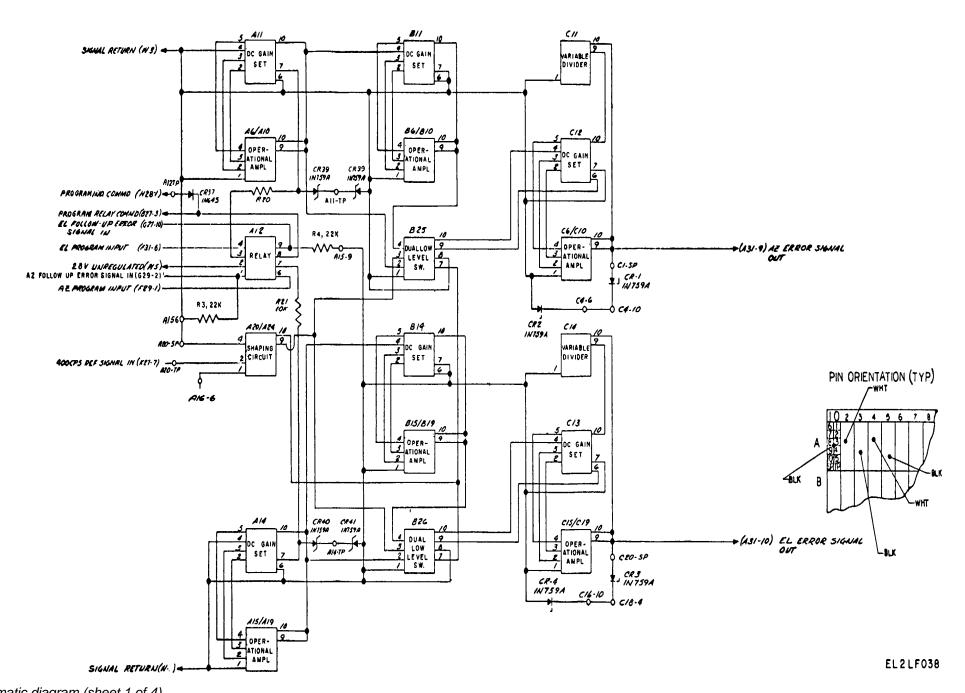

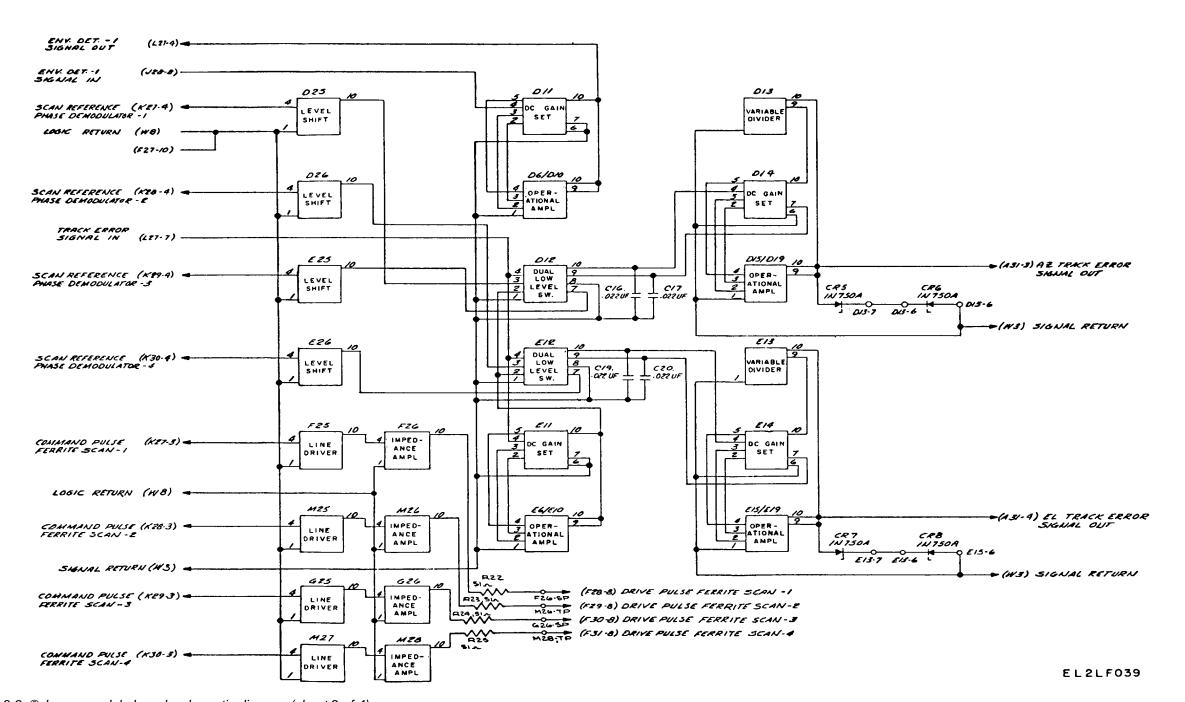

| FO 3-6                 | Azimuth and elevation servo mechanism, schematic diagram                                           |                        |

| FO 3-7                 | Upper module board, schematic diagram (7 sheets)                                                   |                        |

| FO 3-8                 | Upper module board, logic diagram (2 sheets)                                                       | Back of manual         |

| FO 3-9                 | Lower module board, schematic diagram (4 sheets)                                                   | Back of manual         |

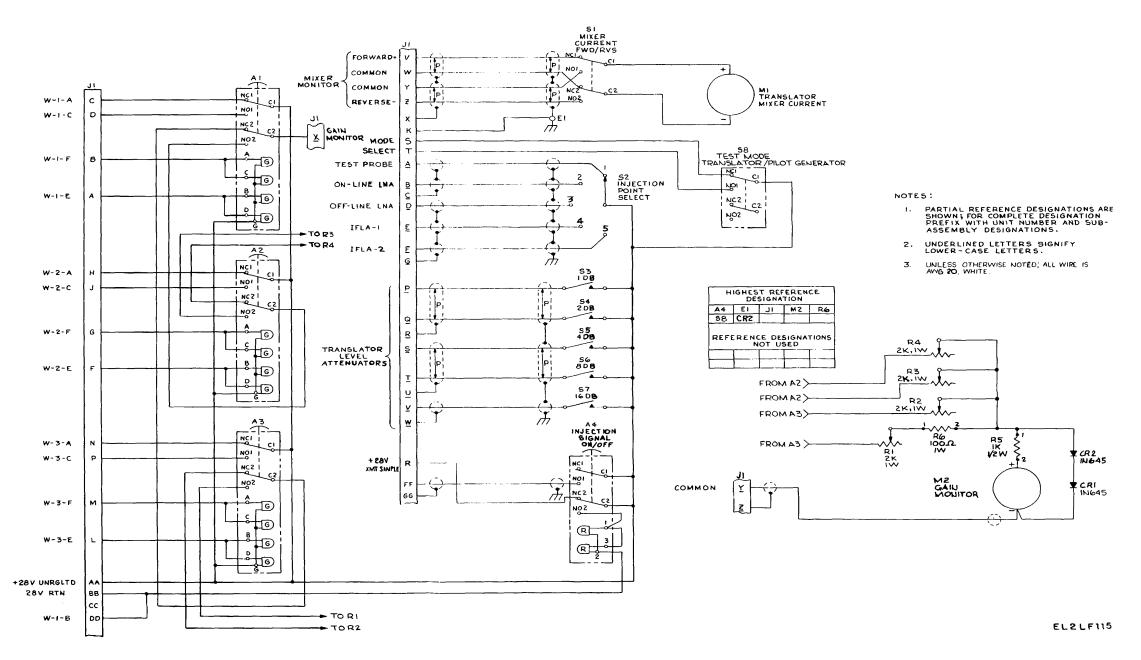

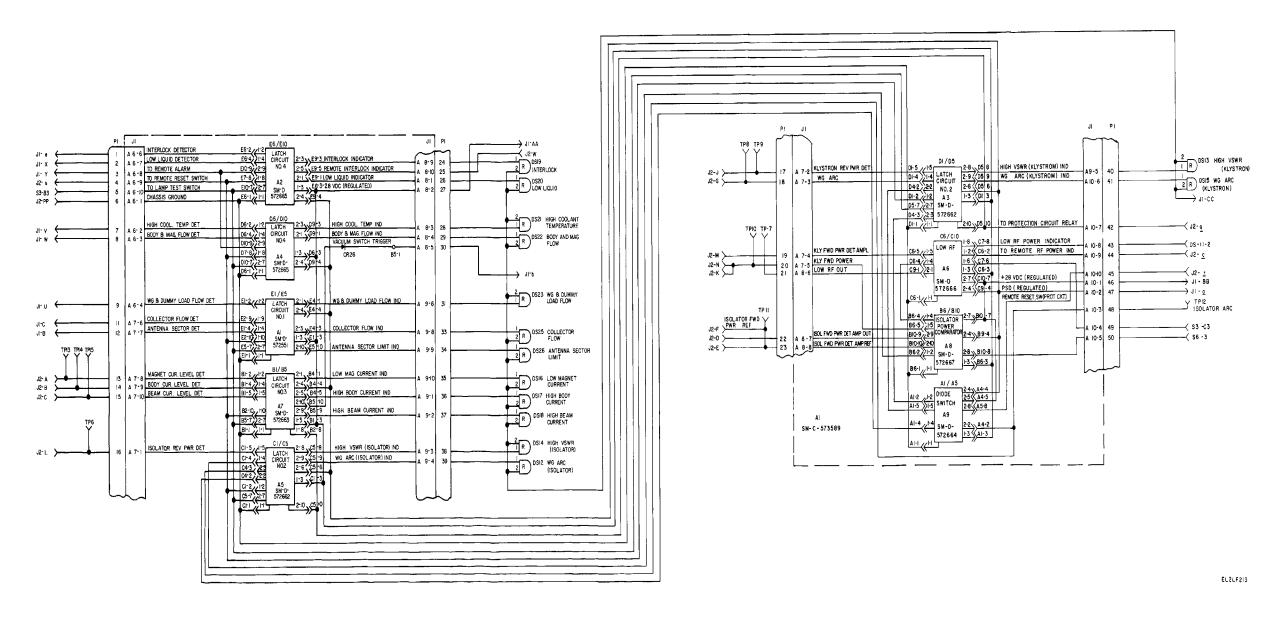

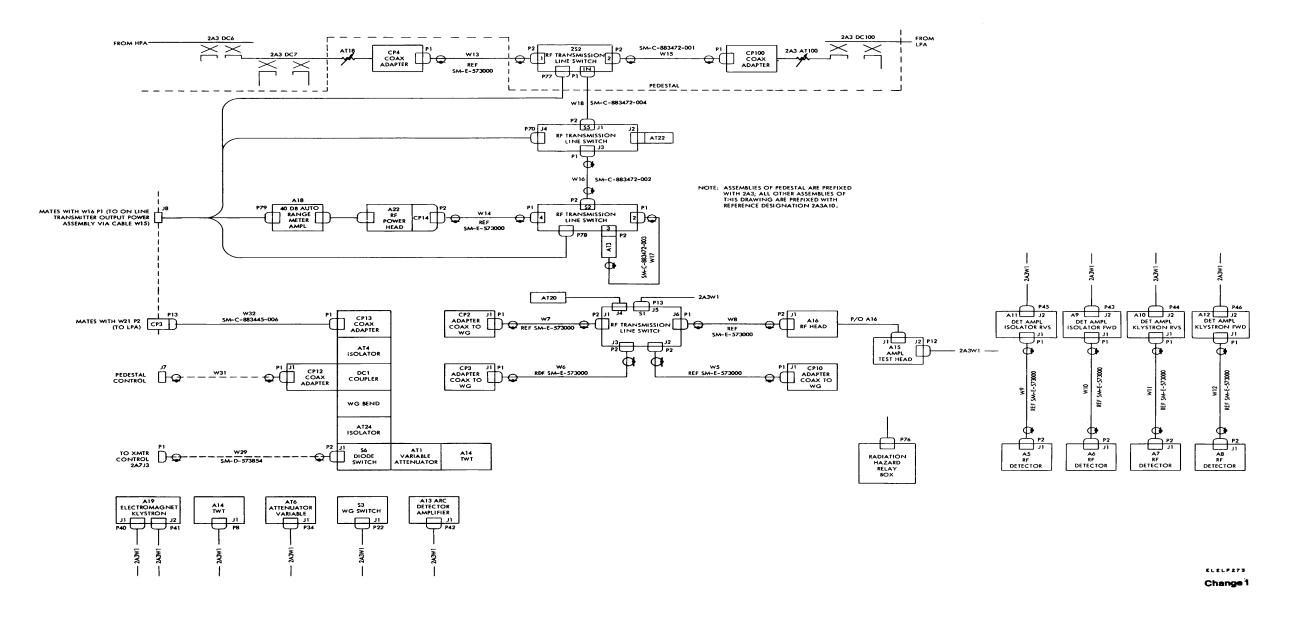

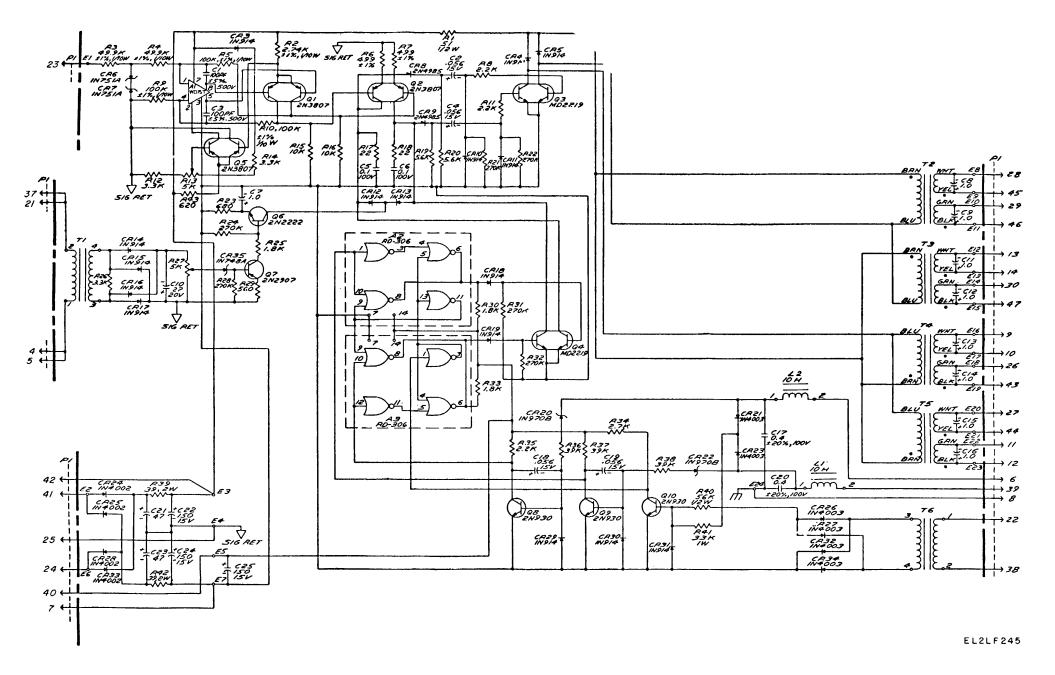

| FO 3-10                | RF power monitor and control 1A2A27, schematic diagram                                             |                        |

| FO 3-10.1<br>FO 3-11   | On line transmitter output power assembly schematic diagram                                        |                        |

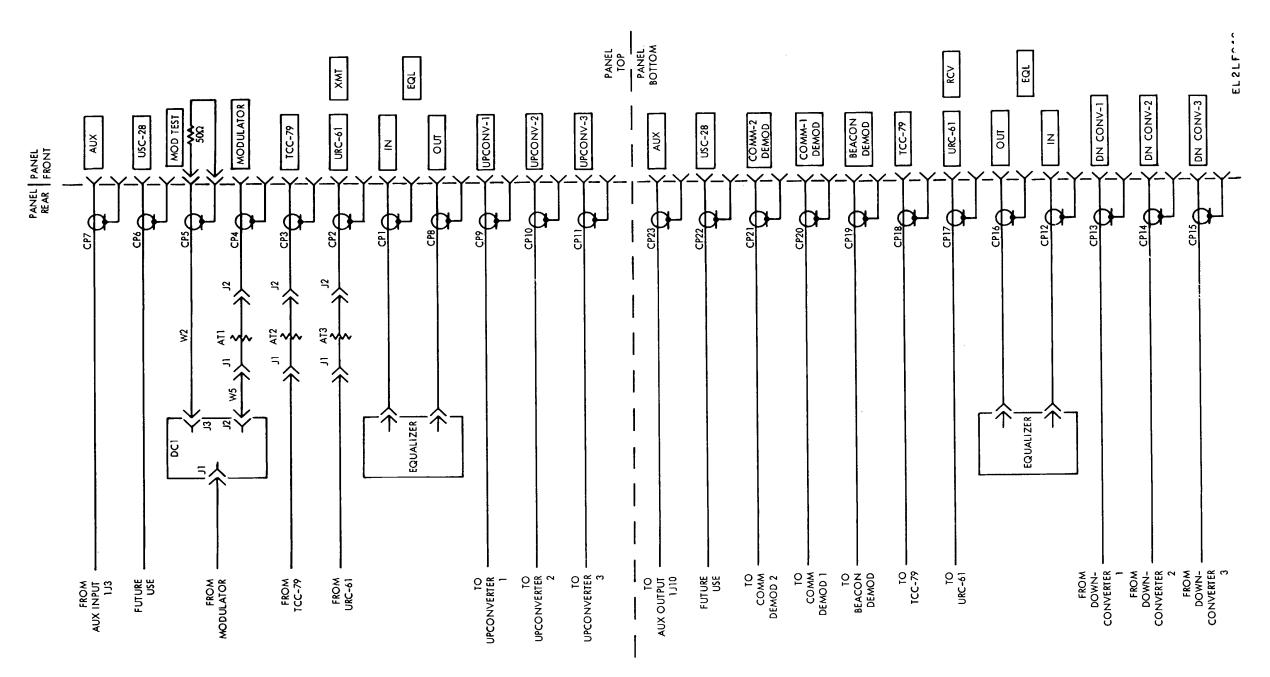

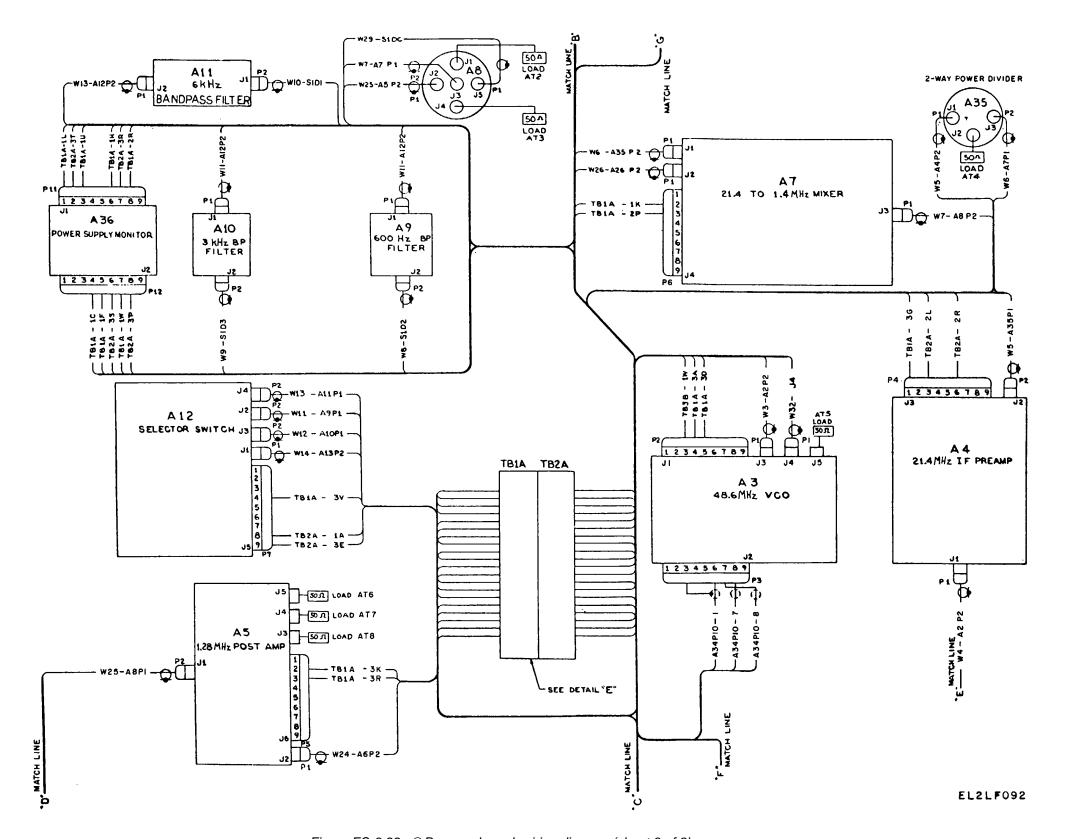

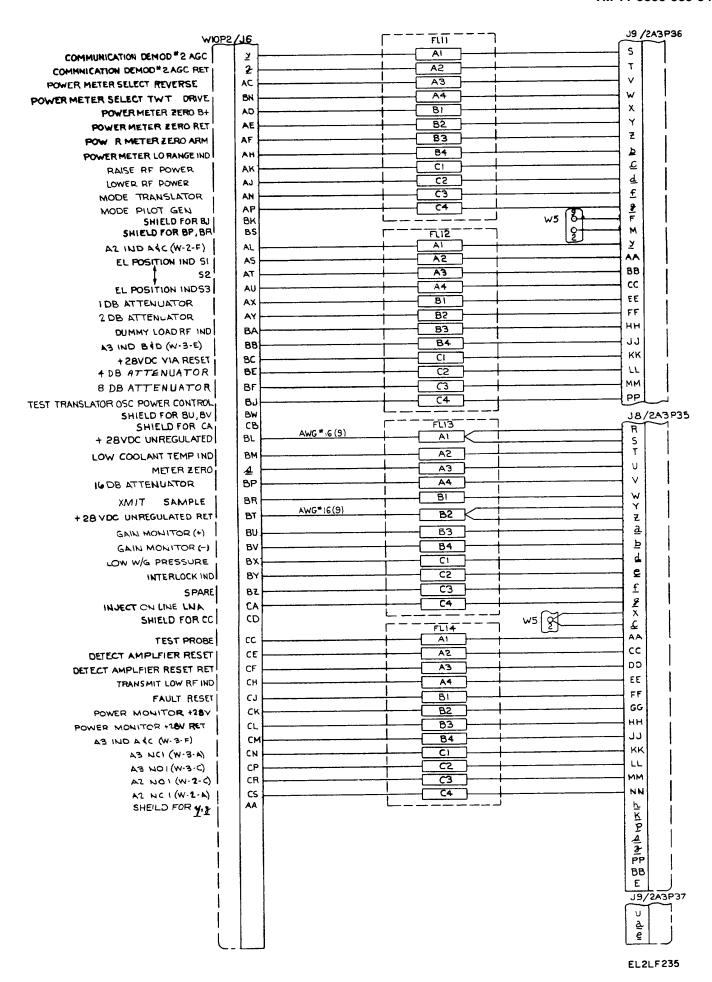

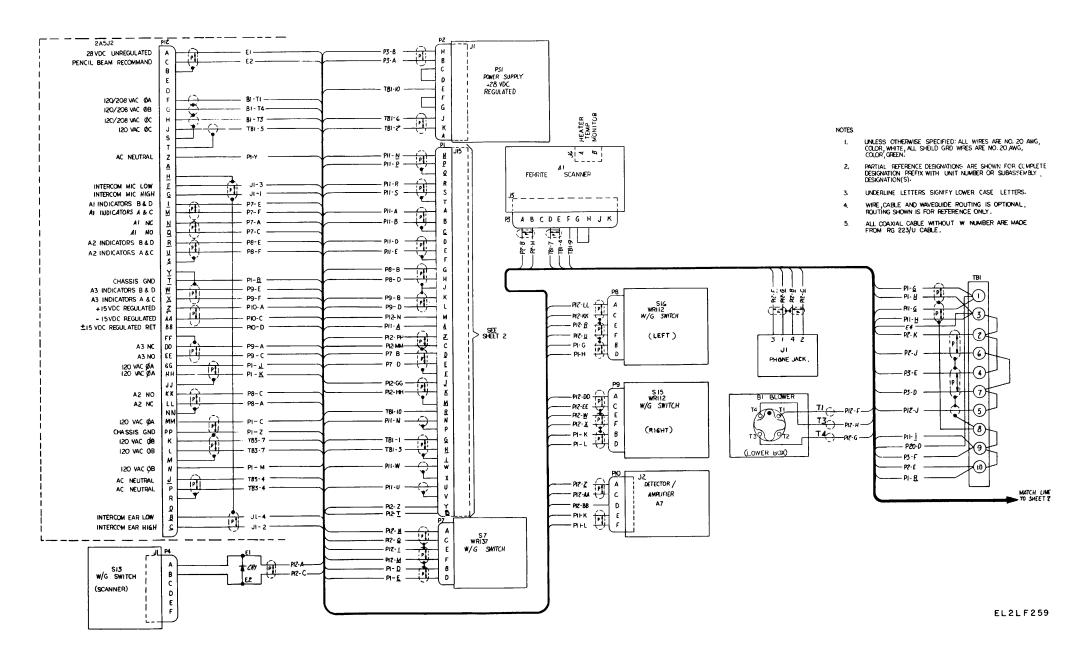

| FO 3-11                | IF patching panel 1A3A22, cabling diagram                                                          |                        |

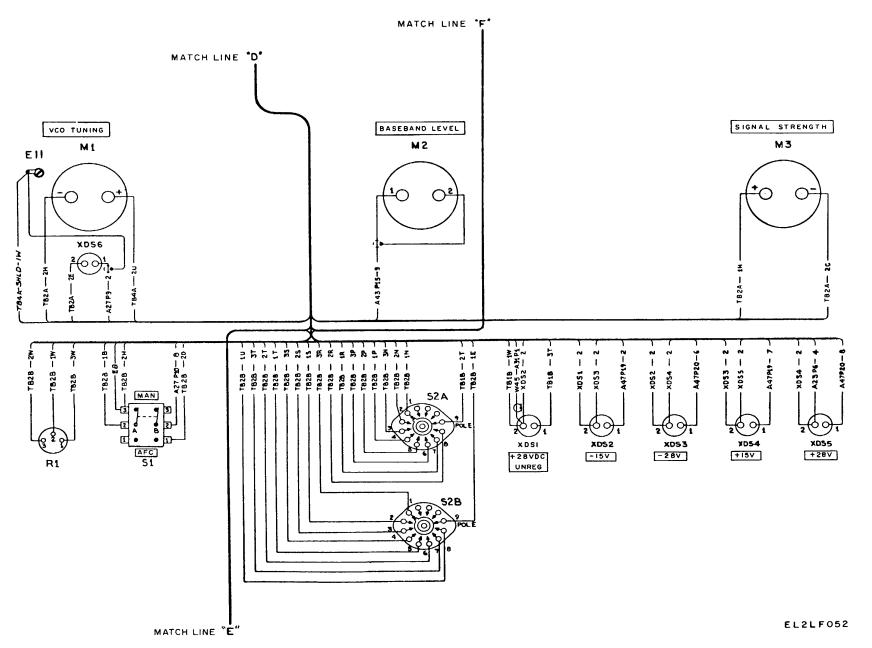

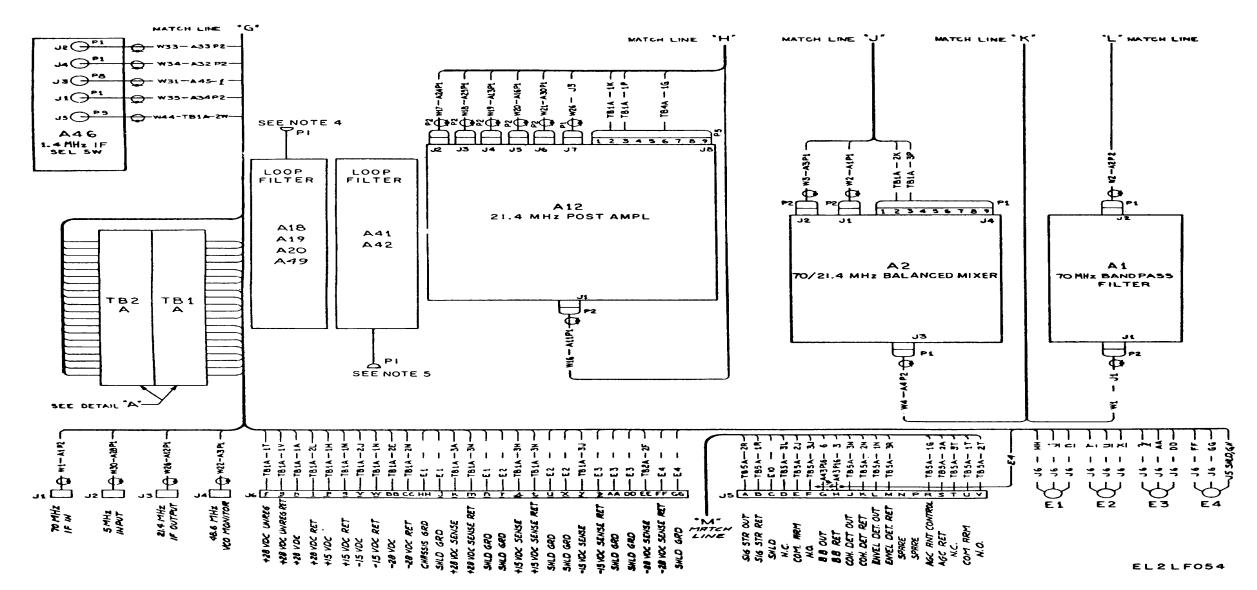

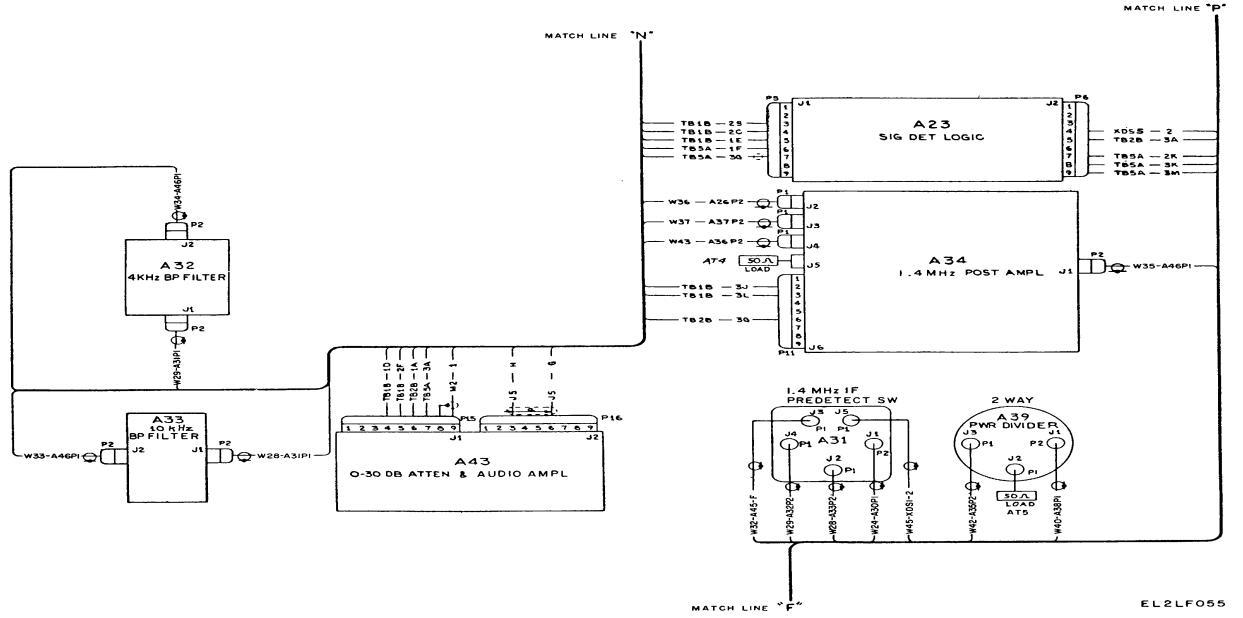

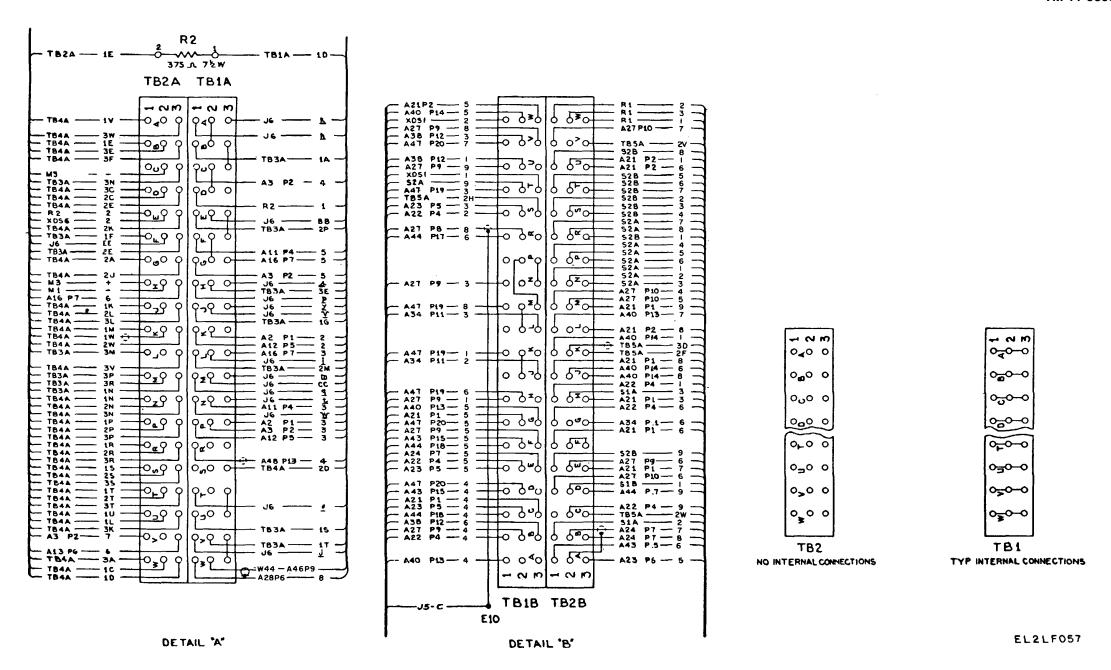

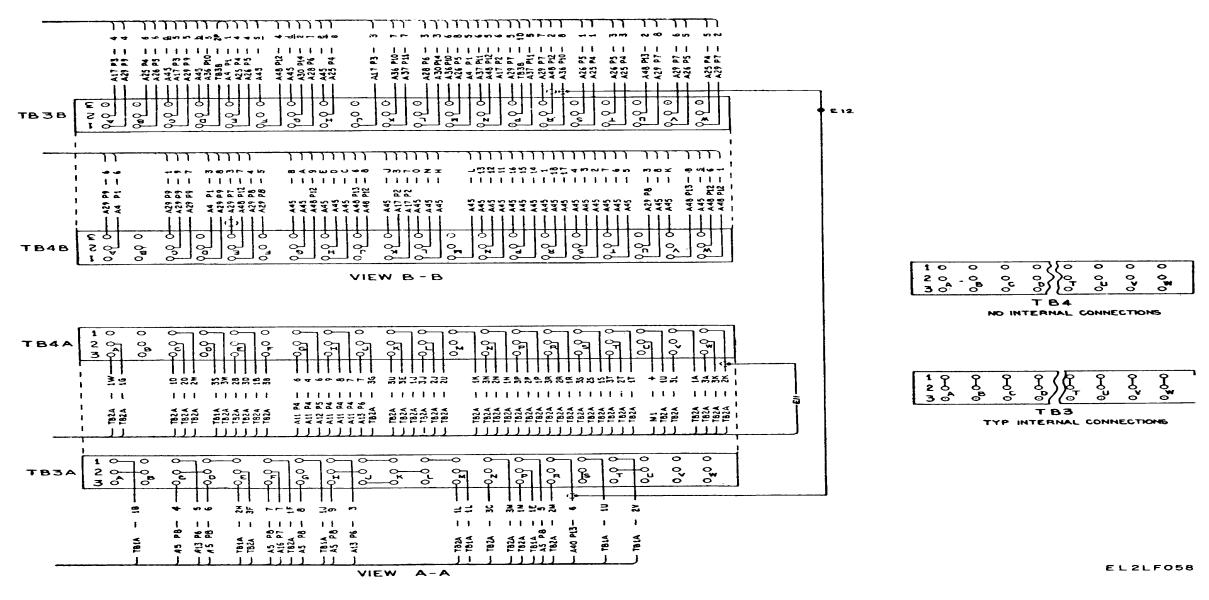

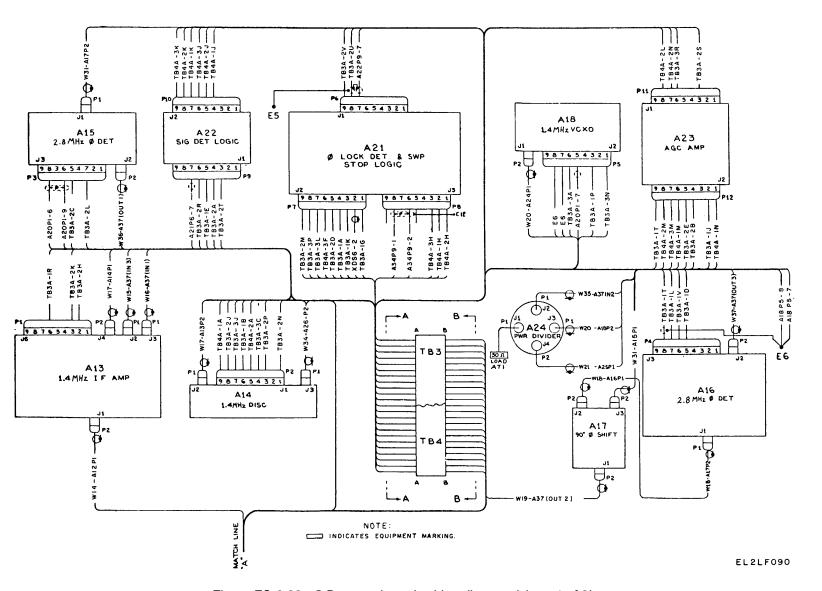

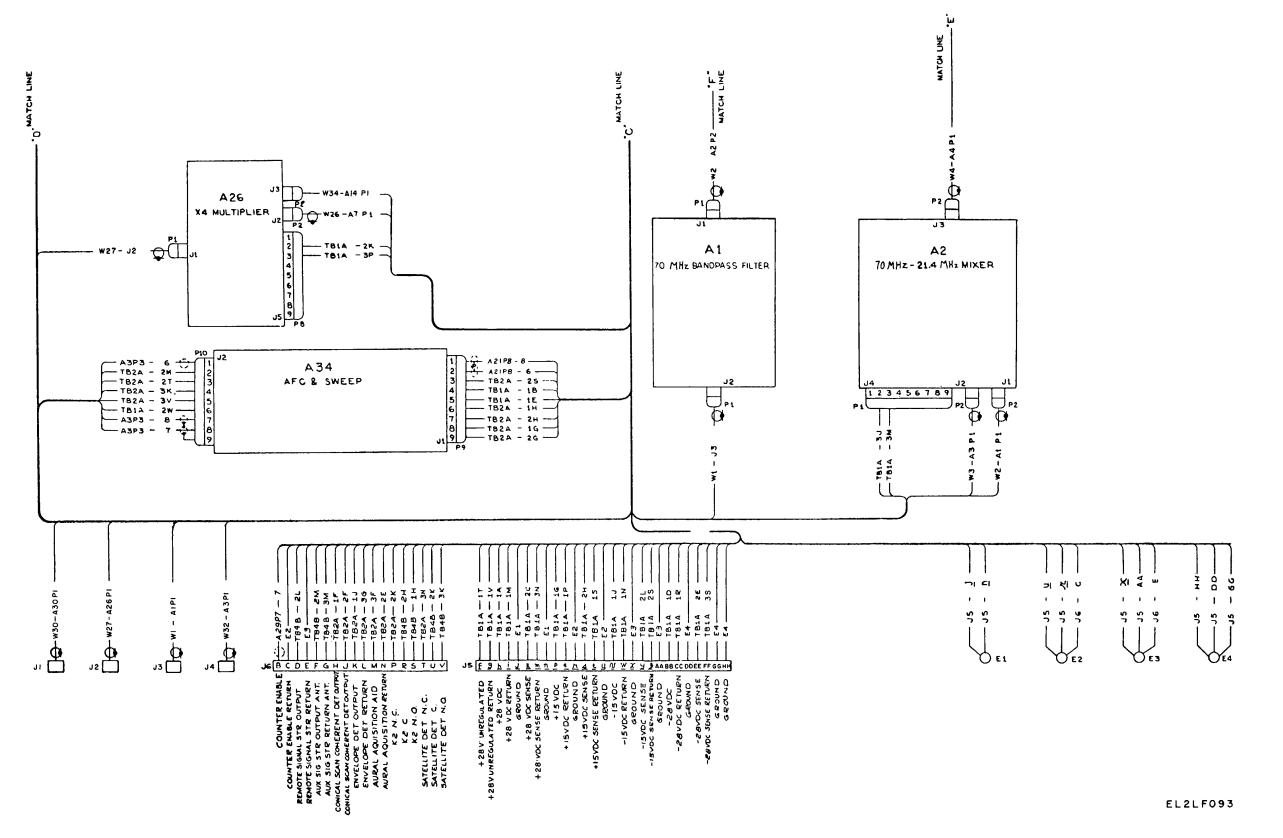

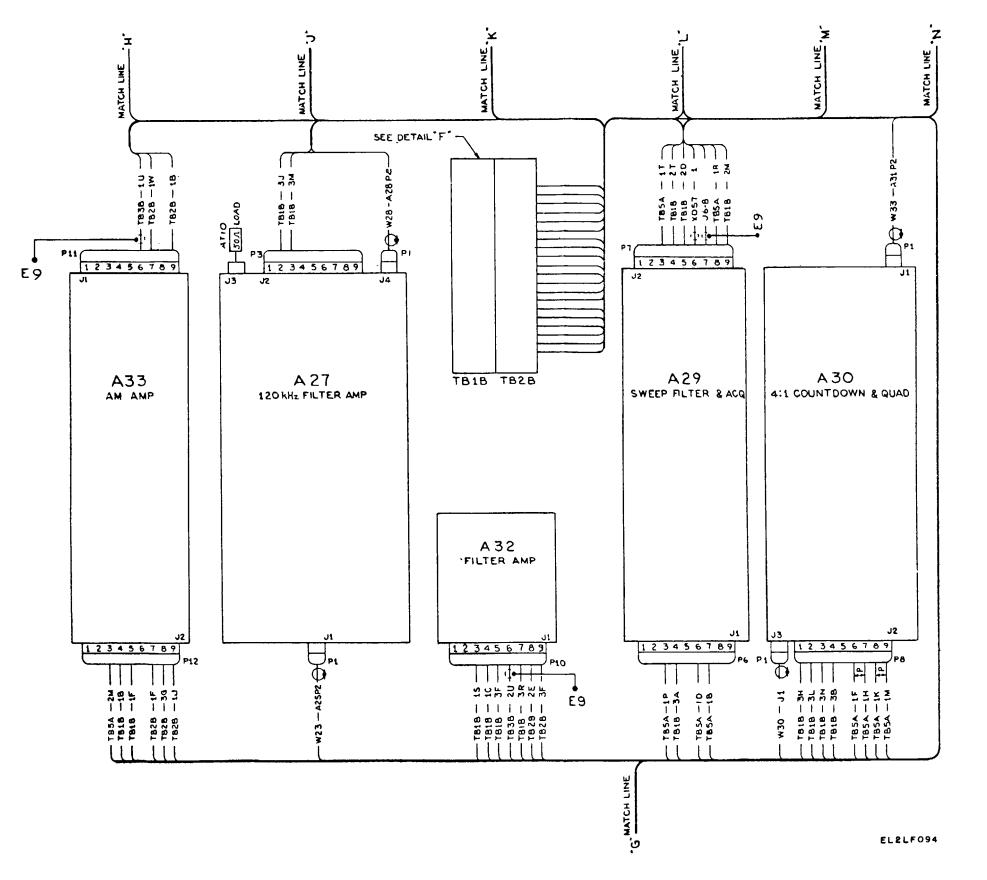

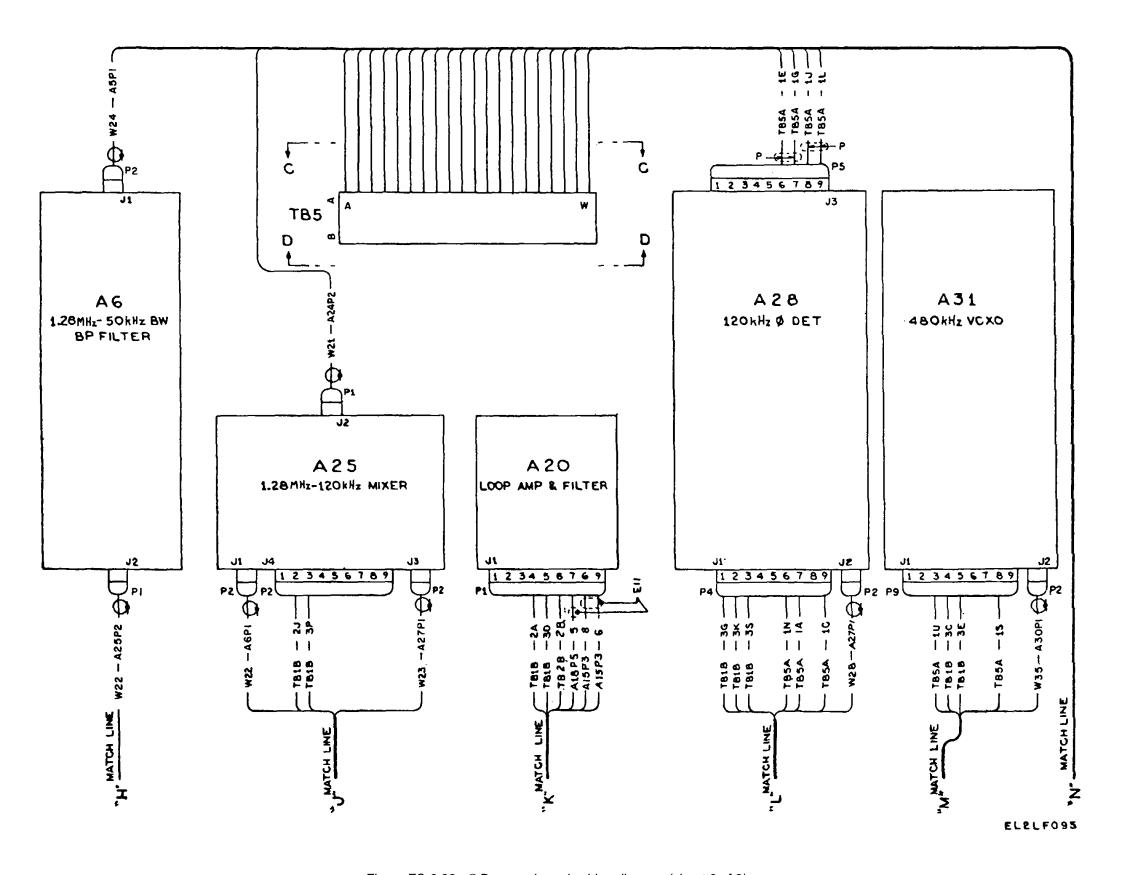

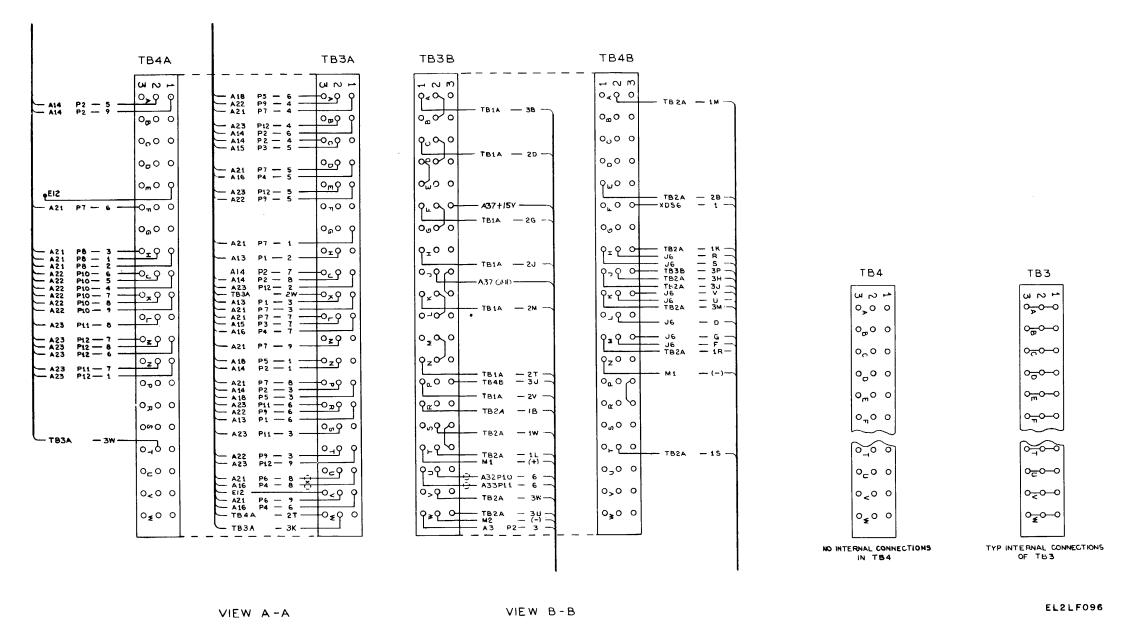

| FO 3-13 <sup>®</sup>   | Comm demod 1A3A3, wiring diagram                                                                   |                        |

| through                |                                                                                                    |                        |

| FO 3-13®               |                                                                                                    |                        |

| FO 3-14                | Demod 48.6 MHz vco A3, schematic diagram                                                           | Back of manual         |

| FO 3-15                | 21.4 MHz if. preamplifier A4, schematic diagram                                                    |                        |

| FO 3-16<br>FO 3-17     | 21.4 MHz post amplifier A12, schematic diagram                                                     |                        |

| FO 3-17<br>FO 3-18     | 21.4 MHz am. phase detector A13, schematic diagram  Demodulator 21.4 MHz vco, schematic diagram    |                        |

| FO 3-19                | X4 frequency multiplier, schematic diagram                                                         |                        |

| FO 3-20                | AFC and sweep circuit, schematic diagram                                                           |                        |

| FO 3-21                | 0-30 dB attenuator and audio amplifier, schematic diagram                                          | Back of manual         |

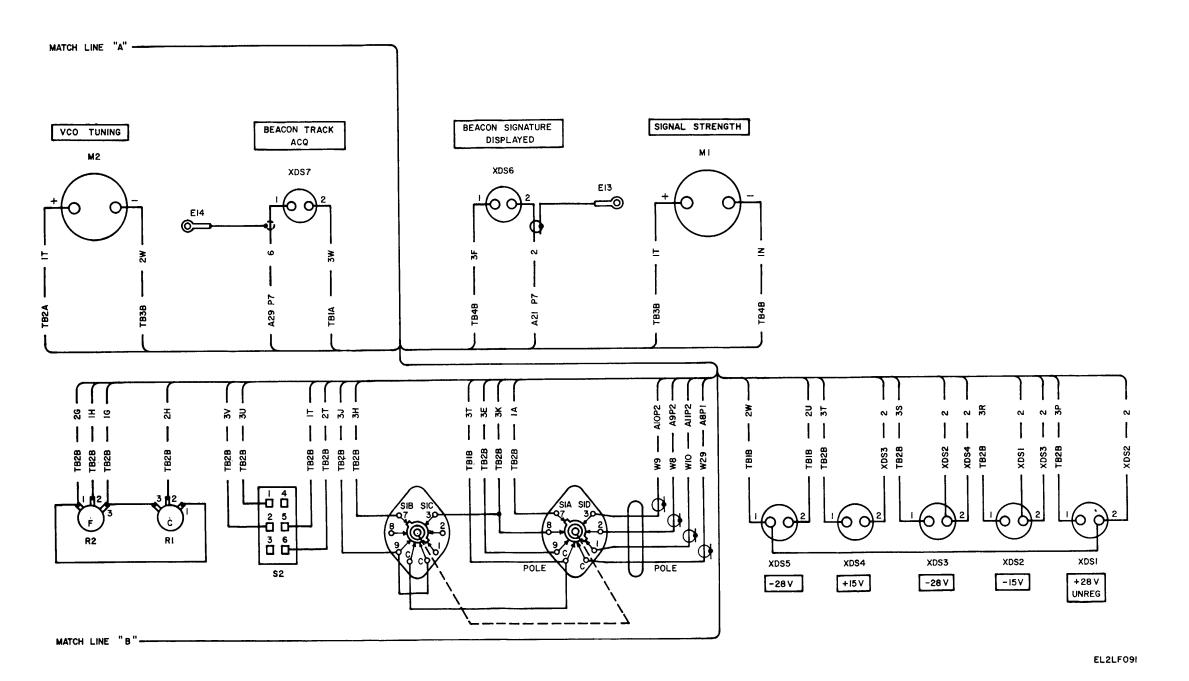

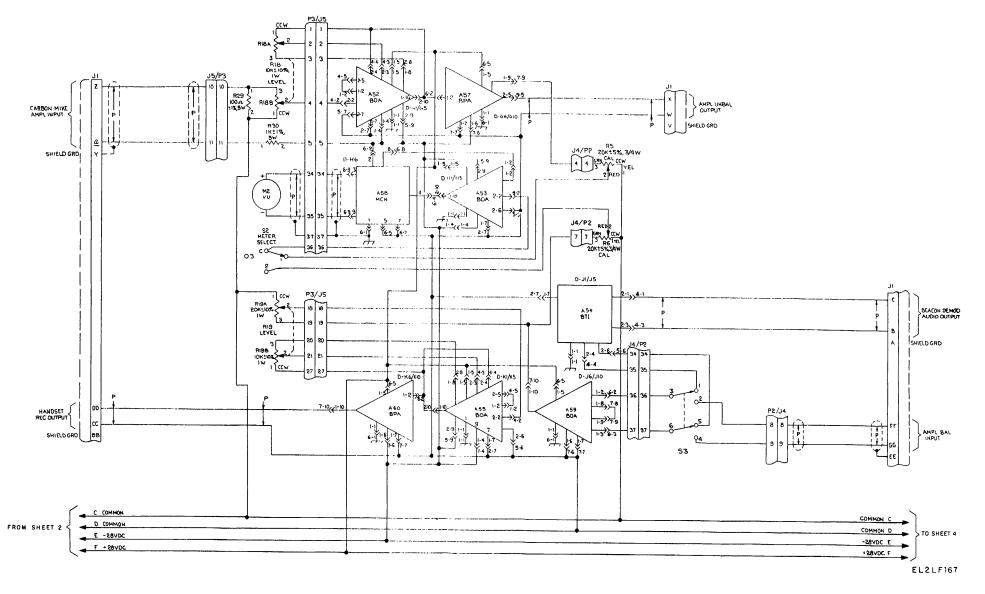

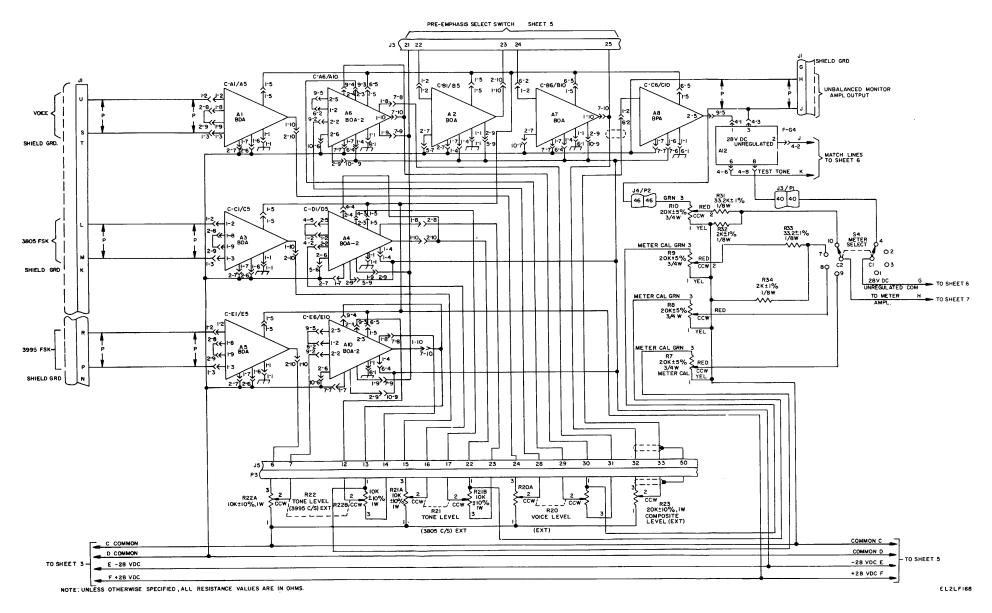

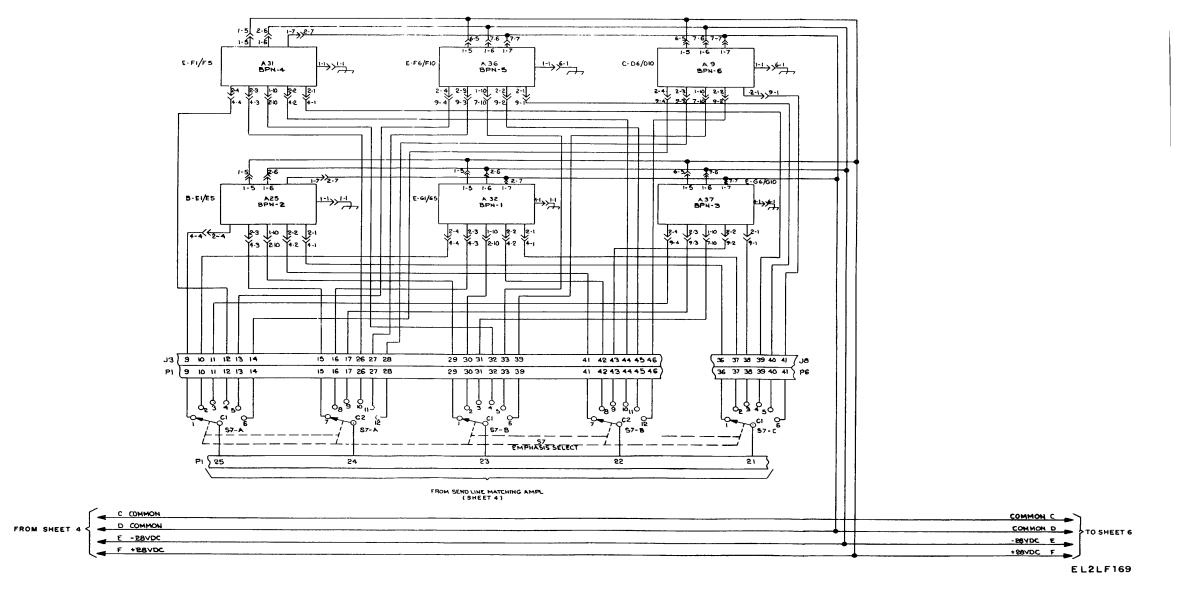

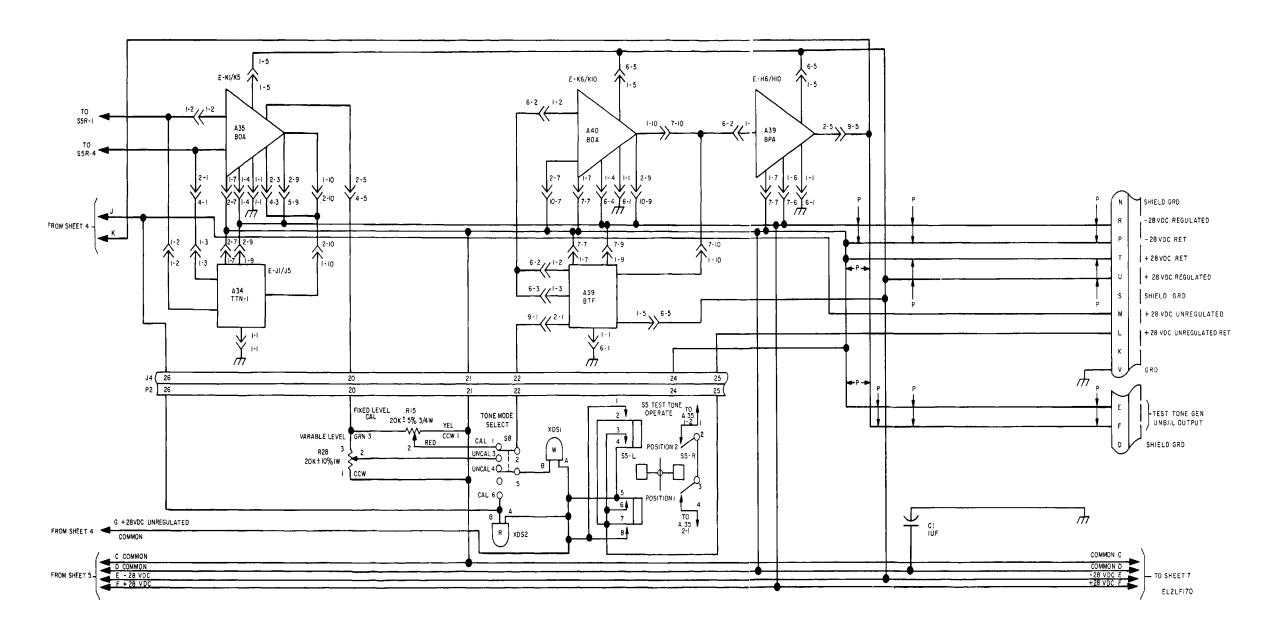

| FO 3-22①               | Beacon demod, wiring diagram                                                                       | Back of manual         |

| through                |                                                                                                    |                        |

| FO 3-229<br>FO 3-23    | 1.4 MHz if. amplifier A13, schematic diagram                                                       | Pook of manual         |

| FO 3-23<br>FO 3-24     | 2.8 MHz phase detector A15/A16, schematic diagram                                                  |                        |

| FO 3-25                | Signal detect circuit A22, schematic diagram                                                       |                        |

| FO 3-26                | 120 kHz filter/amplifier A27, schematic diagram                                                    |                        |

| FO 3-27                | 120 kHz loop phase detector A28, schematic diagram                                                 |                        |

| FO 3-28                | ID sweep, loop filter, and acquisition circuit A29, schematic diagram                              |                        |

| FO 3-29                | ID 4-to-1 countdown and quadrature circuit A30, schematic diagram                                  |                        |

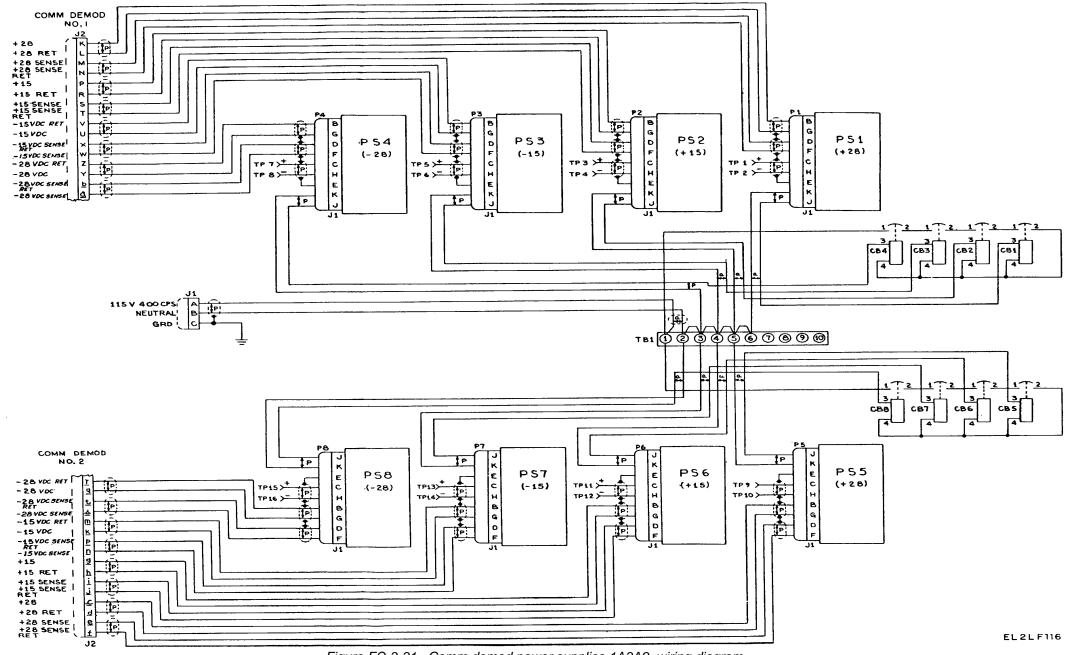

| FO 3-30<br>FO 3-31     | Test translator control 1A2A26, schematic diagram  Comm demod power supplies 1A3A9, wiring diagram |                        |

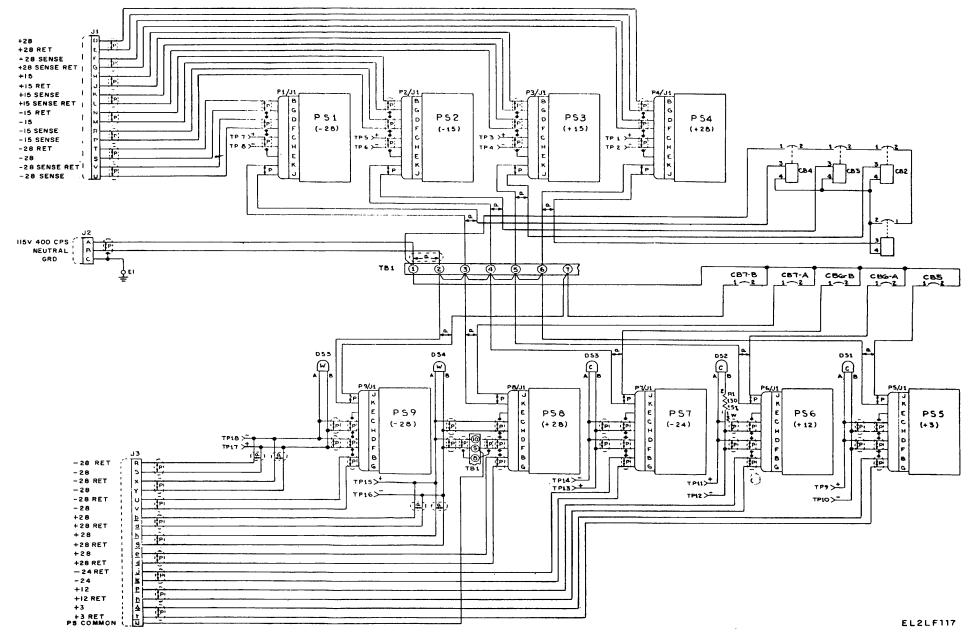

| FO 3-31                | Beacon demod and baseband power supplies 1A3A10, wiring diagram                                    |                        |

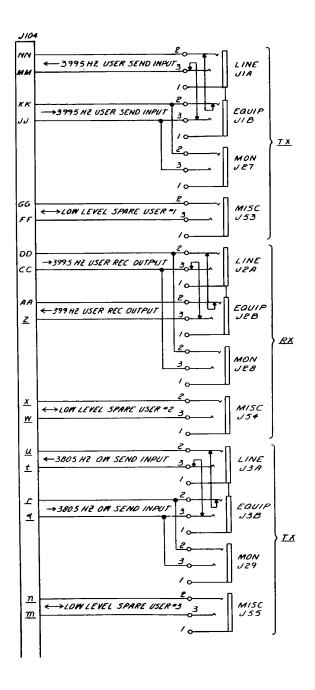

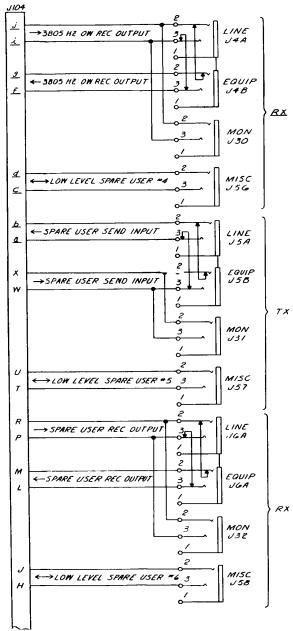

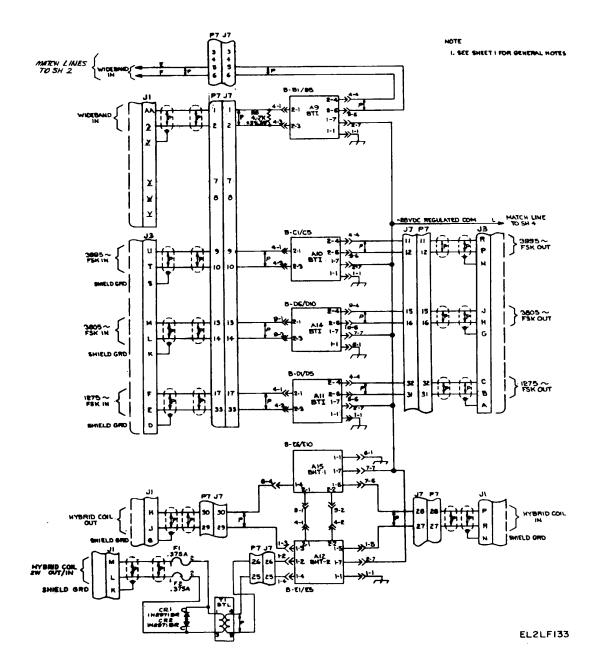

| FO 3-33①               | Teletypewriter patch panel 1A3A25, wiring diagram                                                  |                        |

| through                |                                                                                                    |                        |

| FO 3-33 <sup>(4)</sup> |                                                                                                    |                        |

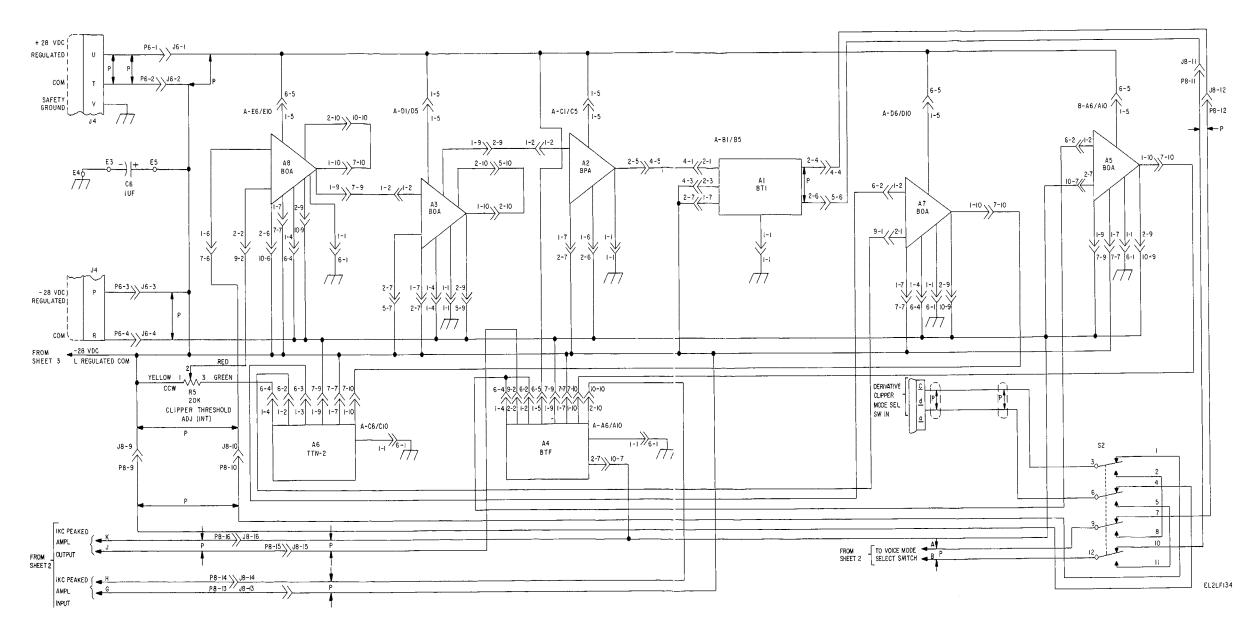

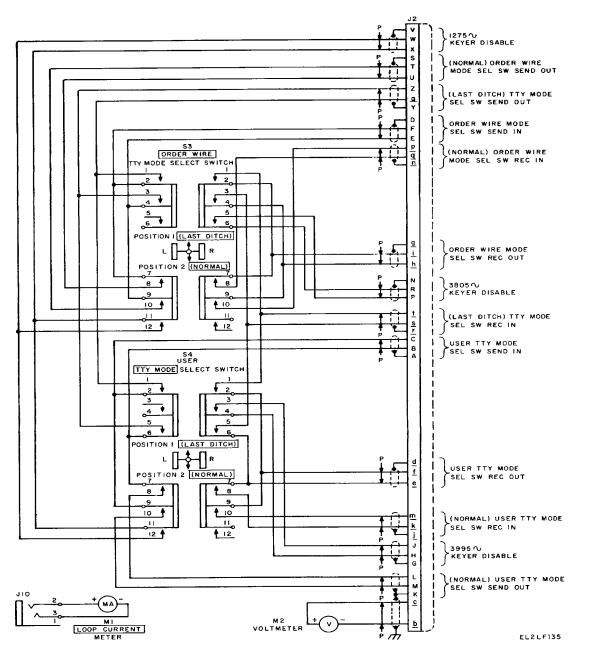

| FO 3-34①               | Baseband control panel 1A3A13, schematic diagram                                                   | Back of manual         |

| through                |                                                                                                    |                        |

| FO 3-34©<br>FO 3-35①   | Modulator 1A3A14, wiring diagram                                                                   | Back of manual         |

| FO 3-35©               | Modulator 1A3A14, wiring diagram                                                                   |                        |

| FO 3-36                | Deviation monitor A14A2, schematic diagram                                                         | Back of manual         |

| FO 3-37                | 10 MHz vco A14A3, schematic diagram                                                                |                        |

| FO 3-38                | Power supply A4, block diagram                                                                     | Back of manual         |

| FO 3-39                | Power supply A4, schematic diagram                                                                 | Back of manual         |

| FO 3-40                | X7 frequency multiplier A6, schematic diagram                                                      |                        |

| FO 3-41                | Divide by 100 frequency and phase detector circuit, schematic diagram                              |                        |

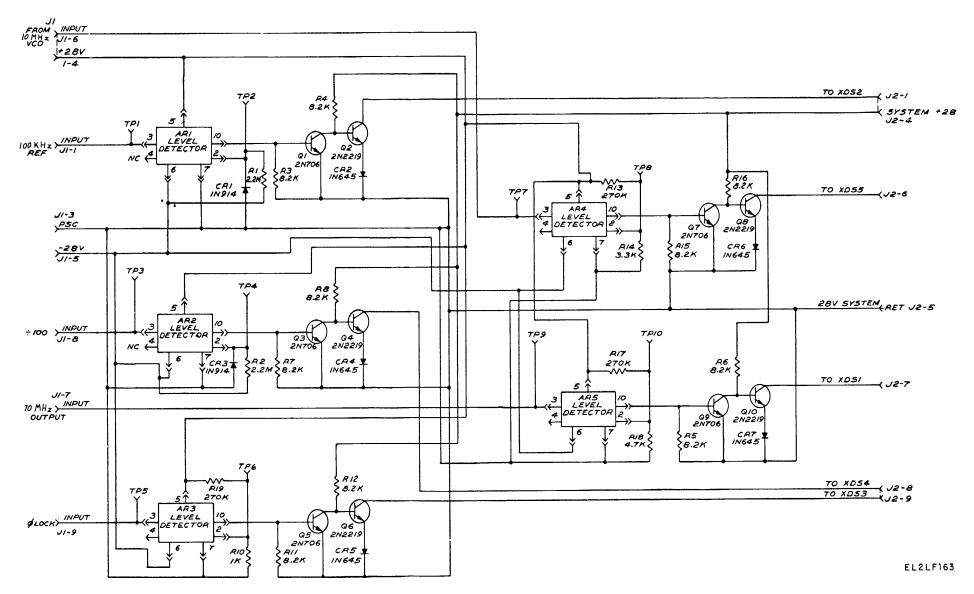

| FO 3-42<br>FO 3-43①    | Level detector and fault lamp driver circuit A8, schematic diagram                                 |                        |

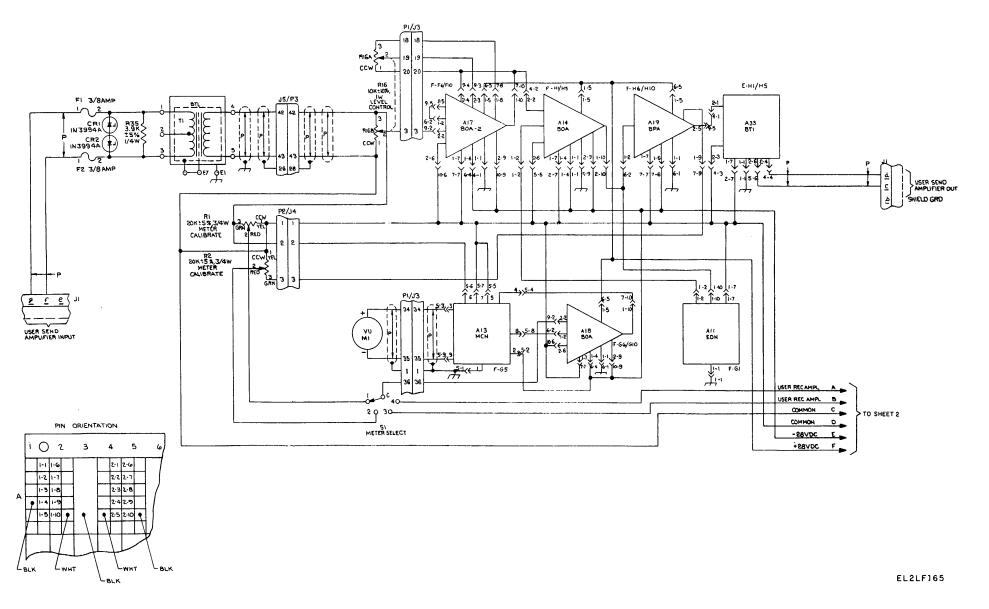

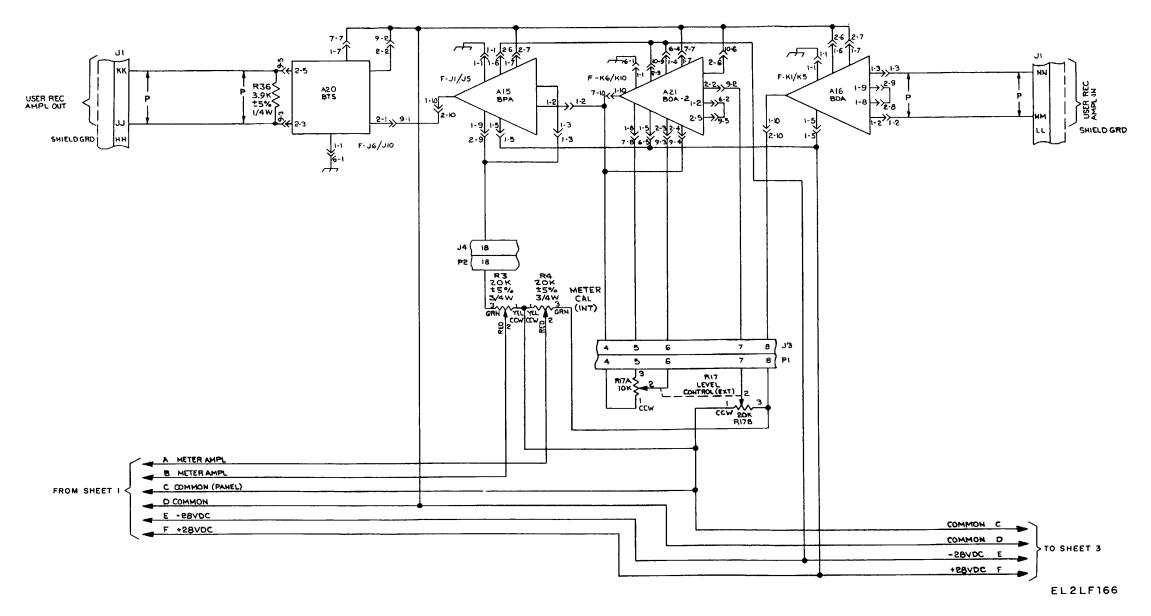

| through                | Dagobana ampililer 170/10, sonematic diagram                                                       | Dack of Illatival      |

| FO 3-43®               |                                                                                                    |                        |

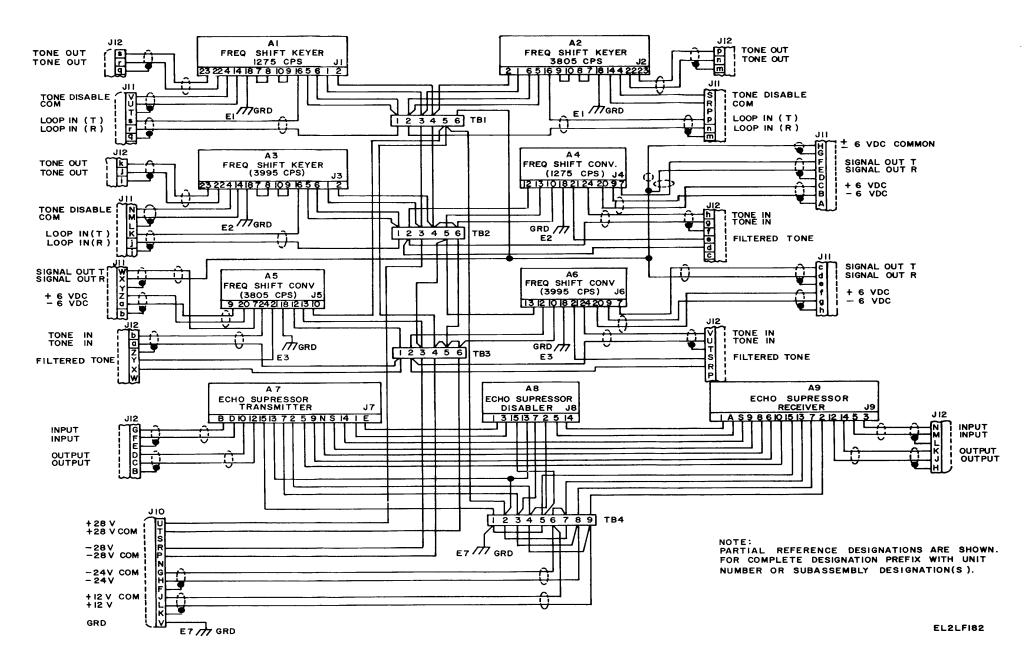

| FO 3-44                | Converter-keyer and echo suppressor 1A3A16, schematic diagram                                      |                        |

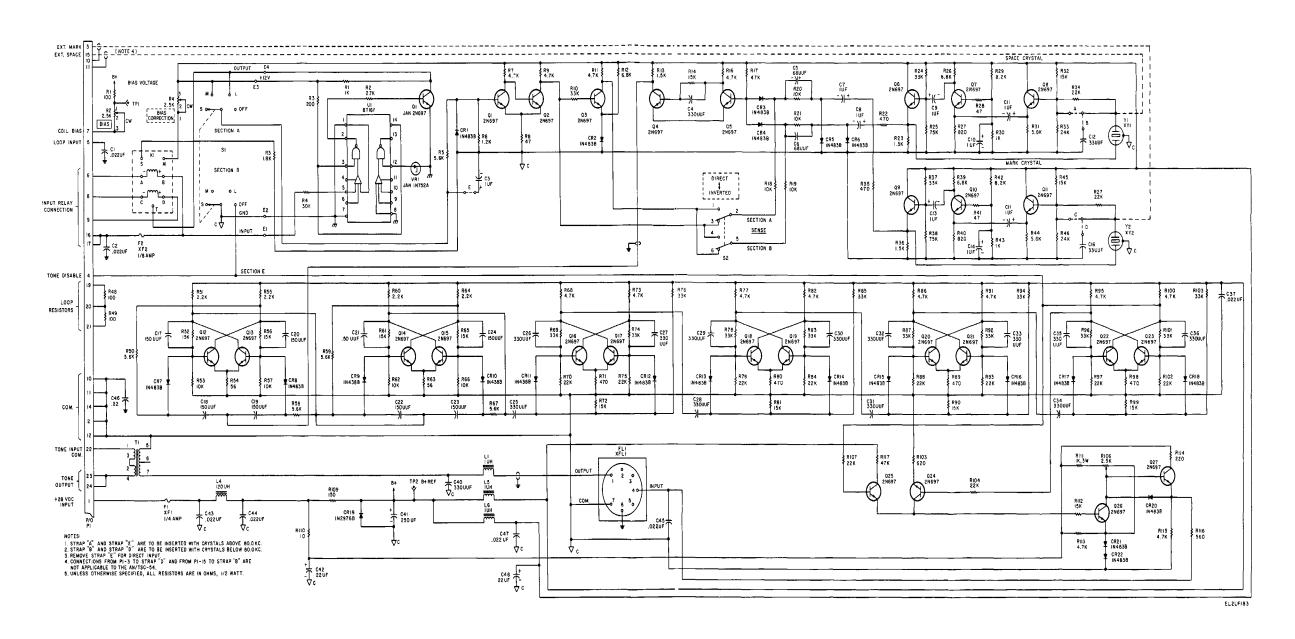

| FO 3-45                | Frequency shift keyer, schematic diagram                                                           | Back of manual         |

| FO 3-46                | Frequency shift converter, schematic diagram                                                       |                        |

| FO 3-47                | Line isolation panel 1A3A26, schematic diagram                                                     | Back of manual         |

| Figure               | Title                                                                | Page           |

|----------------------|----------------------------------------------------------------------|----------------|

| FO 3-48              | 2.0 kw static frequency converter, schematic diagram                 | Back of manual |

| FO 3-49              | Logic assembly AS, schematic diagram                                 |                |

| FO 3-49.1            | OBN monitor panel (1A3A24), schematic diagram                        |                |

| FO 3-50              | Primary power distribution panel 1A1, schematic diagram              |                |

| FO 3-51              | Shelter heater 1A17, schematic diagram                               |                |

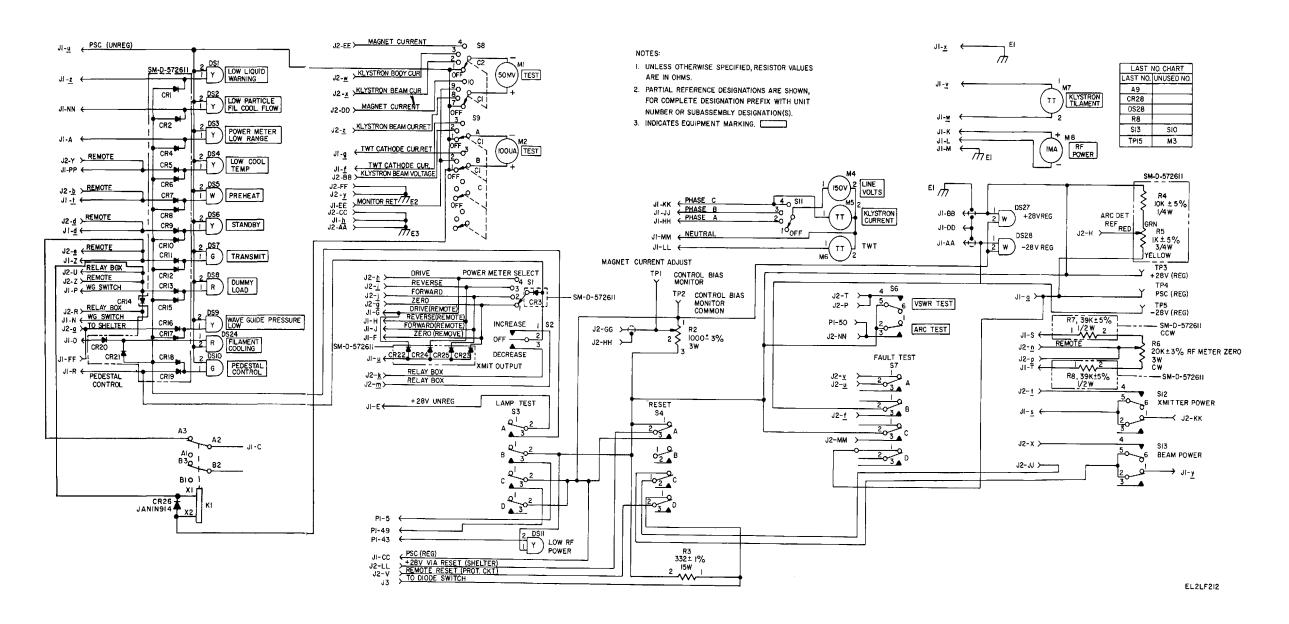

| FO 3-52              | Transmitter control panel, schematic diagram                         |                |

| FO 3-53              | Relay box, schematic diagram                                         |                |

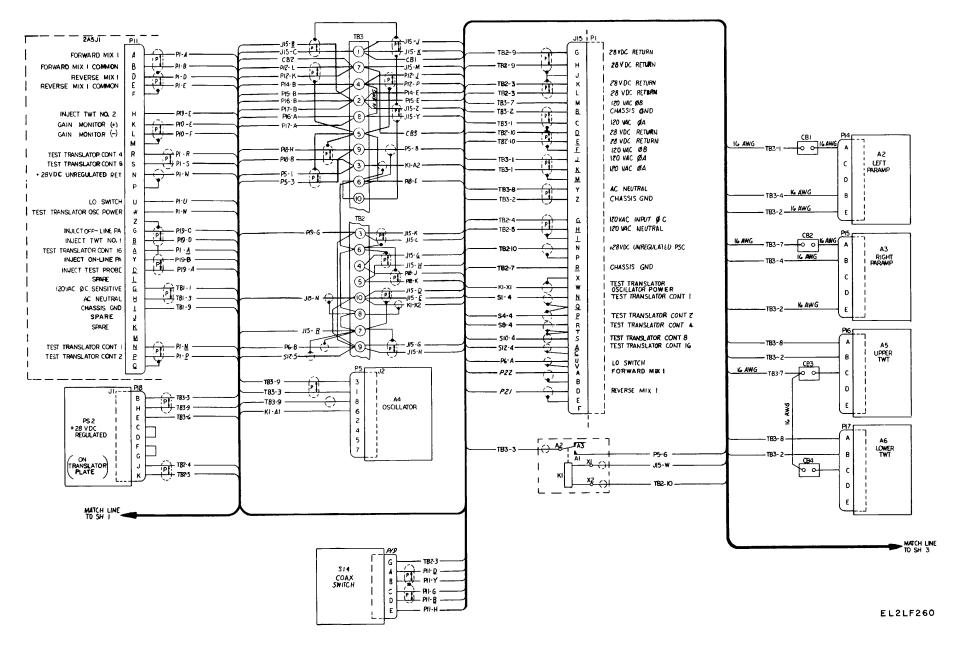

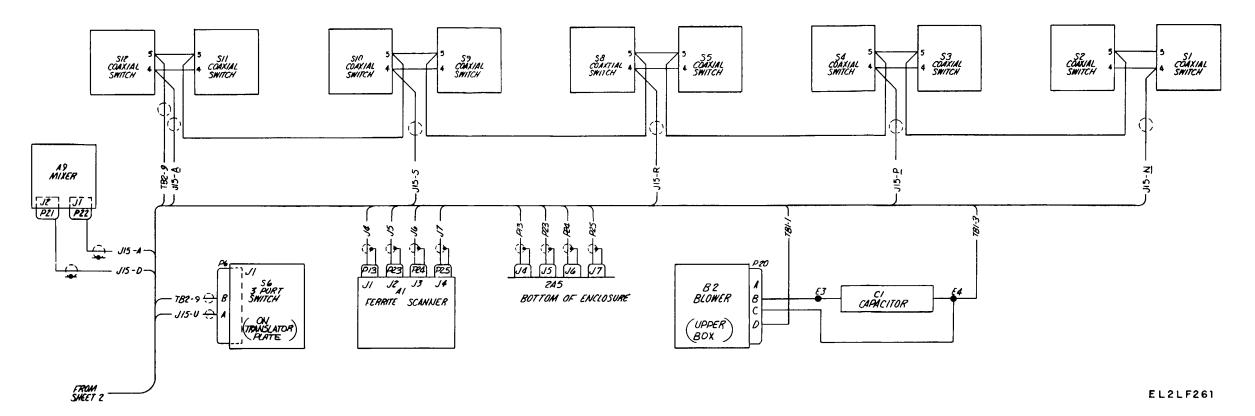

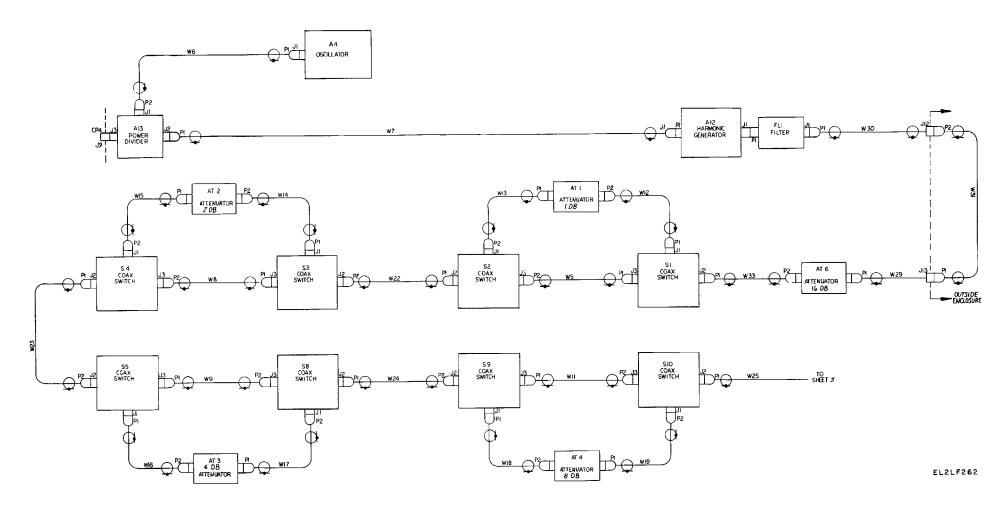

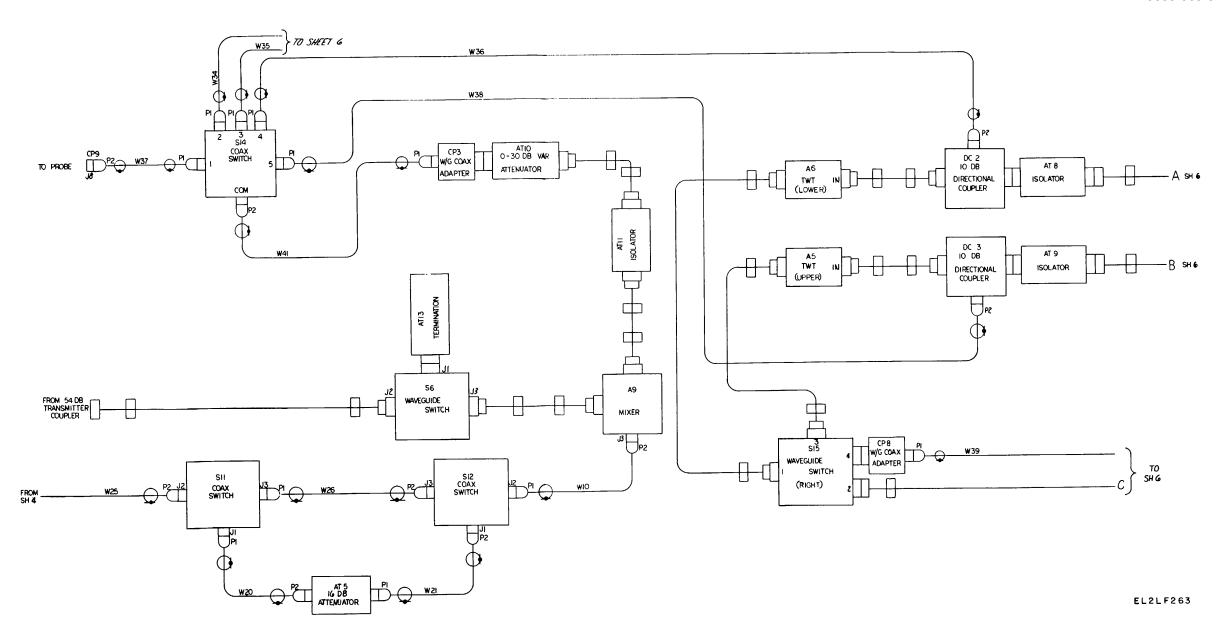

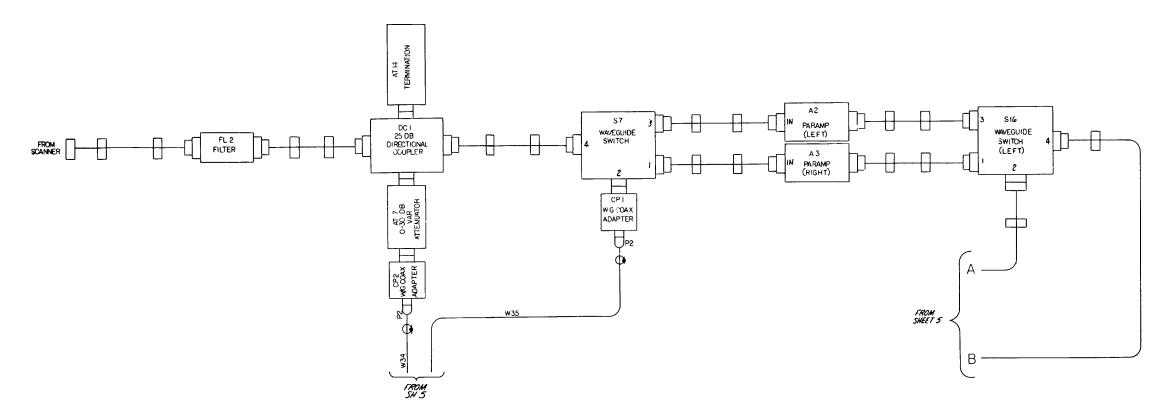

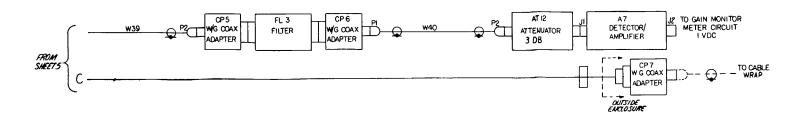

| FO 3-54              | Transmitter/exciter, cabling diagram                                 |                |

| FO 3-55              | High voltage cage, interconnection diagram                           |                |

| FO 3-56 <sup>①</sup> | Primary power distribution panel, wiring diagram                     |                |

| through              |                                                                      |                |

| FO 3-56@             |                                                                      |                |

| FO 3-57              | DC power amplifier component board, schematic diagram                | Back of manual |

| FO 3-58 <sup>①</sup> | RF box, schematic diagram                                            |                |

| through              |                                                                      |                |

| FO 3-56®             |                                                                      |                |

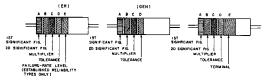

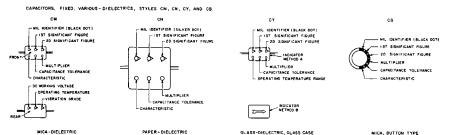

| FO 3-59              | Color code markings for MIL-STD resistors, inductors, and capacitors | Back of manual |

|                      |                                                                      |                |

Change 2 v

### CHAPTER 3 DETAILED CIRCUIT ANALYSIS

#### Section I. COMPONENTS OF OPERATOINS CONTROL VAN

#### 3-1. General

This chapter contains a detailed circuit analysis of Satellite Communication Terminal AN/TSC-54. Many circuit stages of the AN/TSC-54 are functionally identical, differing only in reference designation, component values, or some slight circuit configuration. For purposes of this manual, these stages are considered standard circuits and each stage type described is a fundamental or basic circuit which performs an identical or logical function and is used consistently throughout the Reference designations are arbitrarily equipment. assigned to permit component identification in the general circuit descriptions. Actual designations and values of components may be correlated with a particular stage shown in the applicable schematic diagram.

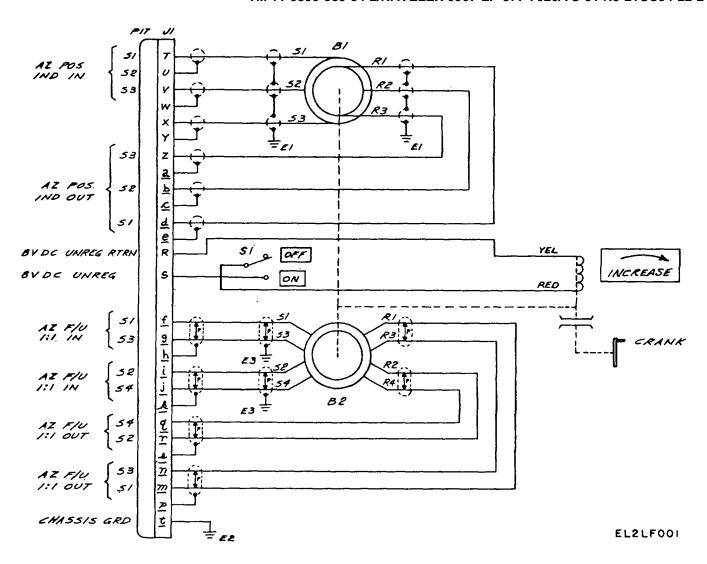

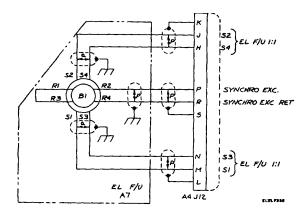

#### 3-2. Zero Set Control 1A2A1

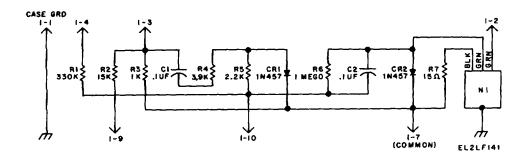

(fig. 3-1)

The zero set control of the AN/TSC-54 is essentially used to position the AZIMUTH digital readout indicators to 0 degrees when the antenna is pointed toward true north. This capability is necessary to compensate for the difference between magnetic north and true north and the difficulty encountered in some locations in aligning the antenna on a true north-south line.

- a. The zero set control includes a synchro, a resolver, a toggle switch, a magnetic clutch, and a handwheel. A signal proportional to antenna position is applied from the azimuth data box resolver to stator windings S1 through S4 of resolver B2. The corrected signal is taken from rotor windings R1 through R4 of resolver B2 and applied to the azimuth followup resolver. The azimuth digital indicator display, which is positioned by the followup circuit, is thus zeroed.

- b. A signal from the azimuth data box synchro, also proportional to antenna position, is applied to stator windings S1 through S3 of synchro B1. The corrected output from rotor windings R1 through R3 is applied to the azimuth position indicator, zeroing it. When power ON-OFF toggle switch S1 is in the ON position, magnetic clutch AI is energized and the AZIMUTH INDICATOR ZERO ADJUST handwheel is engaged. Thus, any rotation of the handwheel turns the synchro and resolver to set in the necessary correction factor.

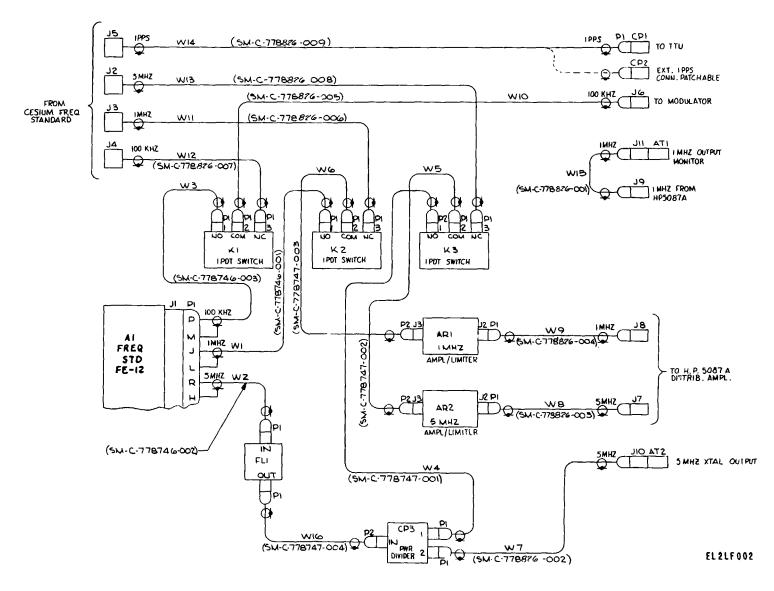

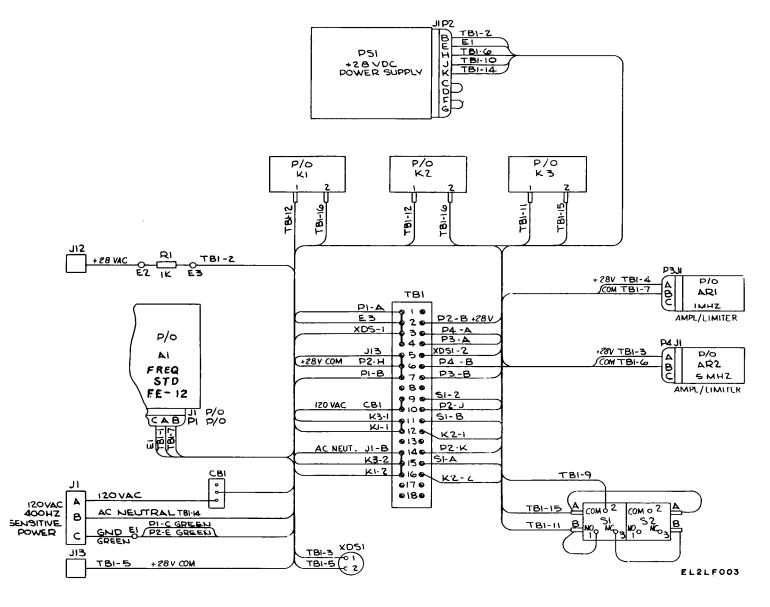

### 3-3. Reference Frequency Generation Equipment

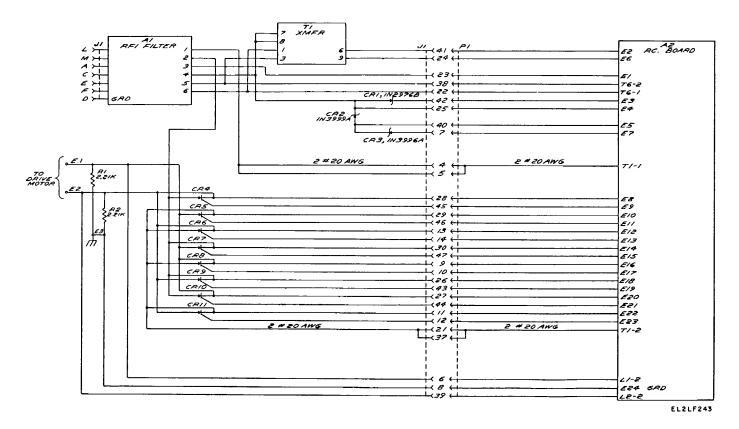

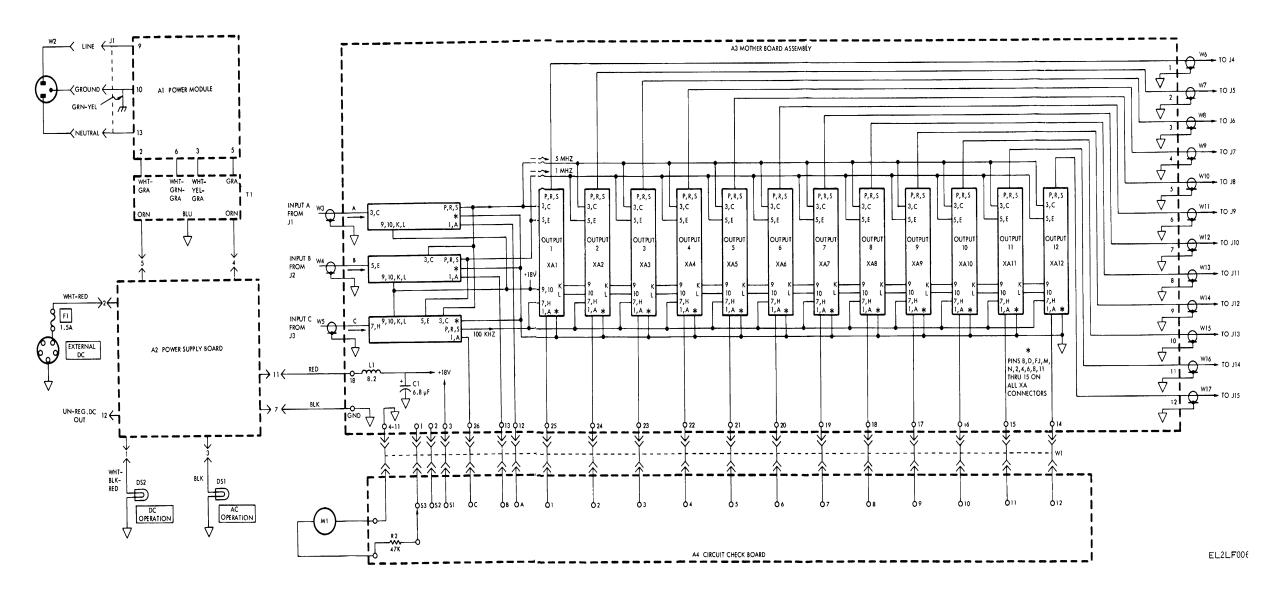

(fig. 3-2 through 3-7, FO 3-1)

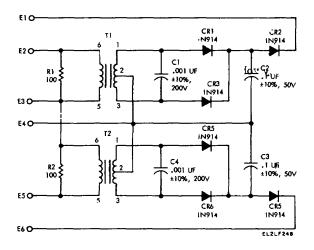

- a. Frequency distribution unit 1A2A22 operates in conjunction with cesium beam standard 1A2A24 and distribution amplifier 1A2A33 to provide accurate, stable mixing and timing signals. The unit consists of an FE-12 frequency standard, filter FL1, coaxial switch assemblies K1, K2, and K3, two-way power divider CP3, power supply PS1, and amplifier/limiters AR1 and AR2. Figure 3-2 is provided as an aid to understanding the relationship of the elements that comprise the frequency generation equipment.

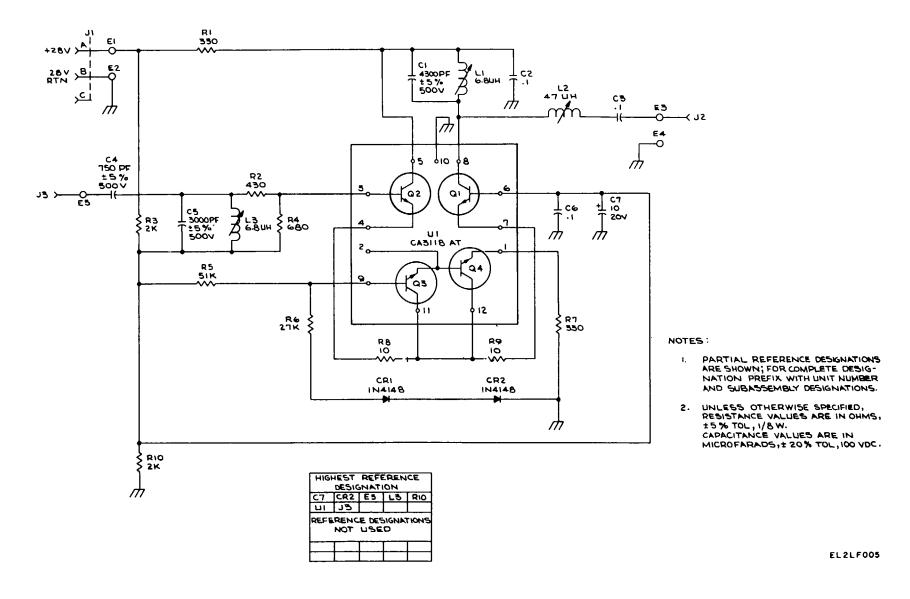

- b. Amplifier/limiters AR1 and AR2 (fig. and 3-4, respectively) are similar in design, the only difference is the frequency response. AR1 contains circuits resonant to 1 MHz, while AR2 contains circuits resonant to 5 MHz. For explanation purposes, refer to the 1 MHz amplifier/limiter schematic diagram (fig. 3-3). The positive 28 vdc operating voltage is applied at J3, is coupled by capacitor C4 to a tank circuit (C5 and L3) resonant to 1 MHz. Resistors R2 and R4 lower the Q of the tank. From both ends of the tank, signals are applied to transistor array U1. The main signal path is from the bottom of the tank to the base of Q1. Limiting occurs by increasing the emitter potential of Q1. This is accomplished by the combined action of transistors Q2, Q3, and Q4, and diodes CR1 and CR2. The parallel tank in the collector circuit of Q1 (C1 and L1) is resonant to 1 MHz. Capacitor C2 decouples the rf from the +28 vdc line. The 1 MHz signal is applied from the collector of Q1, through a series tank (L2 and C3) resonant to 1 MHz, to output connector J2. The preceding explanation is applicable to 5 MHz amplifier/limiter AR2, except that the tank circuits in that assembly are resonant to 5 MHz.

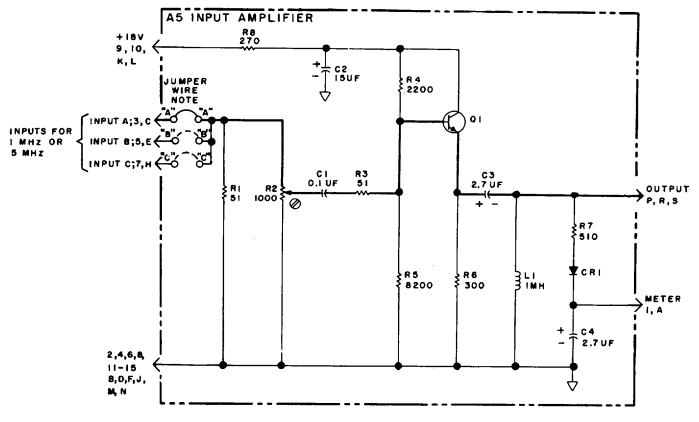

- c. Distribution amplifier (fig. FO 3-1, 3-5 through 3-7) 1A2A33 accepts 1 MHz and 5 MHz signals from frequency distribution unit 1A2A22. The distribution amplifier provides multiple 1 MHz and 5 MHz outputs to major units in the AN/TSC-54. The unit consists of three sections, preamplifier assembly A5, output amplifier assemblies A8 and A9 and power supply assemblies Al and A2. d. The 1 MHz and 5 MHz preamplifiers (fig. 3-5) are identical in design. Inputs to preamplifier as-

- sembly A6 are fed across R2, C1, and R3 to the base of emitter follower Q1. The output of Q1 is fed through coupling capacitor C3 to output connections A6 (P,R,S). A portion of the output signal is developed across R7 and rectified by CR1. The rectified output is available at A5 (1,A) and is displayed on CIRCUIT CHECK meter M1.

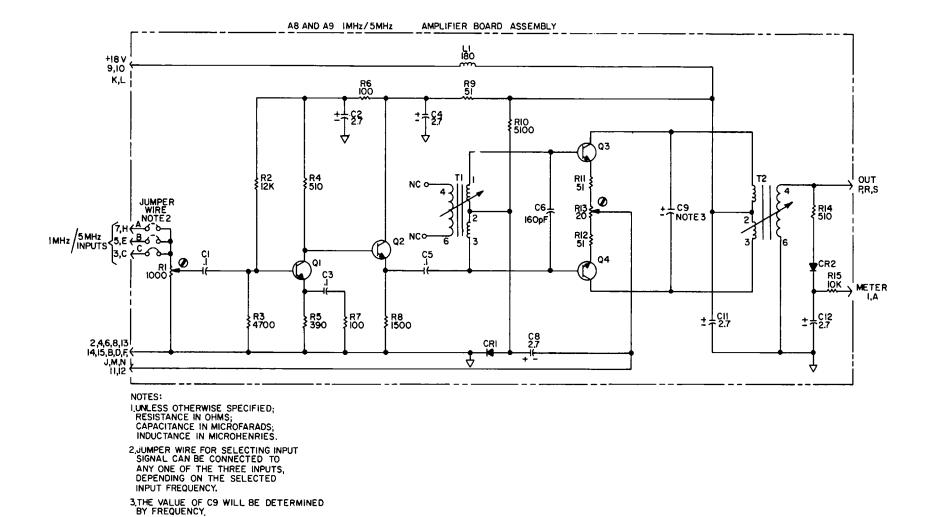

- Output amplifiers A8 and A9 (fig. 3-6) are similar in design, the only difference is the frequency response which is determined by the value of capacitor C9. Input signals are applied through R1 and C1 to the base of Q1. Transistor Q1 amplifies the signal and drives emitter-follower Q2. Transistor Q2 in turn drives push-pull amplifiers Q3 and Q4. The secondary winding of transformer T1 provides the 180° phase shift needed to drive Q3. The Q3, Q4 base input circuit is tuned by T1 secondary winding and C6. Base-bias for Q3 and Q4 is derived from the forward voltage drop of CR1 (17 vdc). Resistor R13 is a dc balance adjustment for Q3 and Q4 and is used to minimize second harmonic distortion in the output signal. Output signals from Q3 and Q4 are transformer coupled through T2 to output connectors P,R,S. A portion of the output signal is developed across R14 and rectified by CR2. The rectified output is available at output connection 1,A and is displayed on CIRCUIT CHECK meter M1.

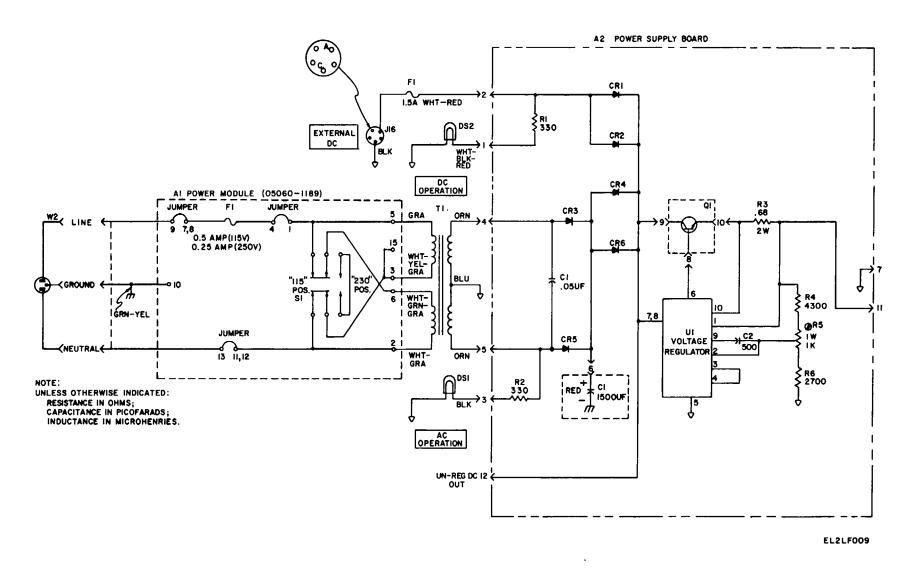

- The power supply section is comprised of power module A1 and power supply A2 (fig. Module A1 contains the ac input connector, 115/240 vac select switch S1 and line fuse F1. The ac input is fed through the Al to the primary of transformer T1. The signal at the secondary of T1 is rectified by CR3 and CR5 and filtered by C1. A portion of the ac signal is developed across R2 and is used to illuminate AC OPERATION lamp DS1. The filtered dc is applied through dc blocking diodes CR4 and CR6 to the input of voltage regulator U7 (7,8) and series regulator Q1. Voltage regulator U1 initially allows Q1 to conduct. The output voltage at the junction of R3 and R4 is sensed through divider R4, 5 and 6 at U1 (2). Regulator U1 controls the voltage at the base of Q1 which controls current flow through Q1 and regulates the output voltage to the load. The voltage drop across R3 is monitored by U1 (10,1)to provide current limiting protection. When the voltage drop across R3 becomes excessive. U1 detects it and biases Q1 off. Normal operation is returned when the excessive load is removed from the power supply.

Figure 3-1. Zero set control 1A2A1, schematic diagram.

Figure 3-2. Frequency distribution unit 1A2A22, connection diagram (sheet 1 of 2)

Figure 3-2. © Frequency distribution unit 1A2A22, connection diagram (sheet 2 of 2)

Figure 3-3. 1MHz amplifier/limiter 1A2A22AR1, schematic diagram.

NOTES:

#### PARTIAL REFERENCE DESIGNATIONS ARE SHOWN; FOR COMPLETE DESIG-NATION PREFIX WITH UNIT NUMBER AND SUBASSEMBLY DESIGNATIONS. 2. UNLESS OTHERWISE SPECIFIED, RESISTANCE VALUES ARE IN OHMS, RI 330 15% TOL, 1/8 W. CAPACITANCE VALUES ARE IN CI 820 PF ±5 % 500V MICROFARADS, ± 10% TOL, 100 VDC. <u>ع</u>ر ZBV CS LI I-5UH 6.8 N<sup>H</sup> СЭ // h C4 180 PF ±5% 500V 910 R2 GΙ 10 10 20V C6 C5 510 PF 1:5% 500V ) 1.5UH ٠1 R4 2K \$470 uТ TA BITEAD **R**5 Q4 SIK Q3 27K R7 450 R8 R9 10 CRZ CRI IN4148 1N4148 /TRIO 2K EL2LF004

Figure 3-4. 5 MHz amplifier/limiter 1A2A22AR2, schematic diagram

#### NOTES:

RESISTANCES ARE IN OHMS, CAPACITANCES ARE IN PF, INDUCTANCES ARE IN MH.

I. UNLESS OTHERWISE INDICATED, 2. JUMPER WIRE FOR SELECTING INPUT SIGNAL SOURCE CONNECTION DEPENDS ON INPUT SOCKET IN WHICH BOARD IS INSTALLED AND DESIRED SIGNAL SOURCE CONNECTION SHOWN IS FOR USE IN SOCKET A WITH INPUT FROM INPUT JACK JI (INPUT A).

EL2LF007

Figure 3-5. Preamplifier 1A2A33A5, schematic diagram.

EL2LF008

Figure 3-6. Output amplifier 1A2A33A8, schematic diagram.

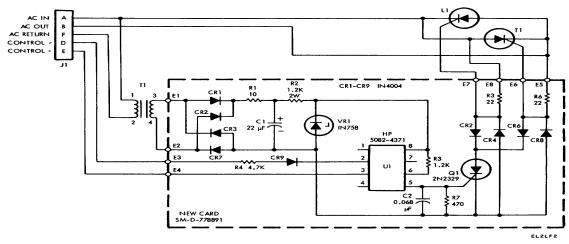

Figure 3-7. Power section 1A2A33A1 and 1A2A33A2, schematic diagram.

#### 3-4. Power Supply Circuit Analysis

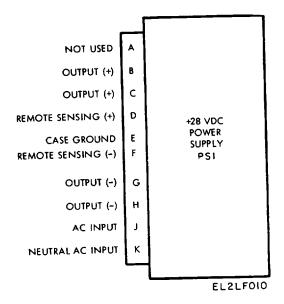

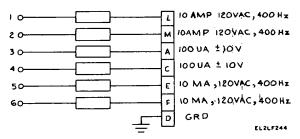

The input and output signal characteristics for +28 vdc power supply pS1, +200 vdc power supply PS2, and +6 vdc power supply PS3 are illustrated in figure 3-8.

Figure 3-8. Plus 28 vdc power supply PS1, input/output signal characteristics.

# 3-5. Power Distribution Panel 1A2A4 Components

(fig. FO 3-2 and 3-9)

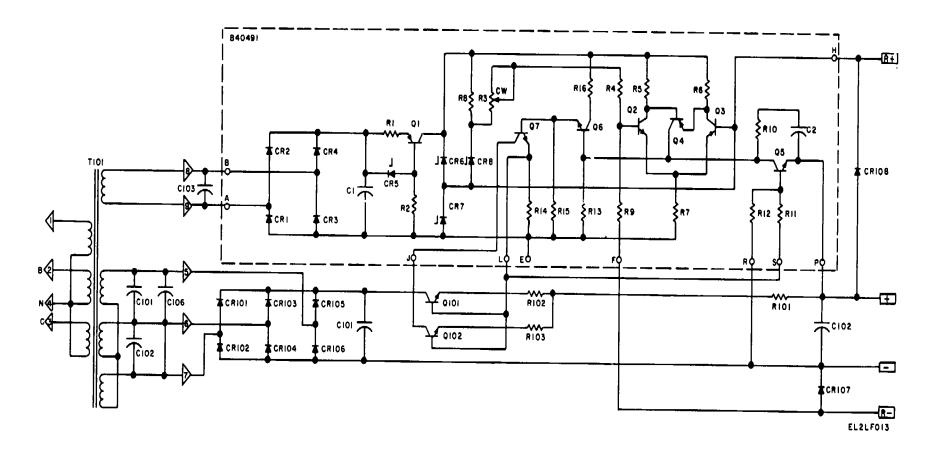

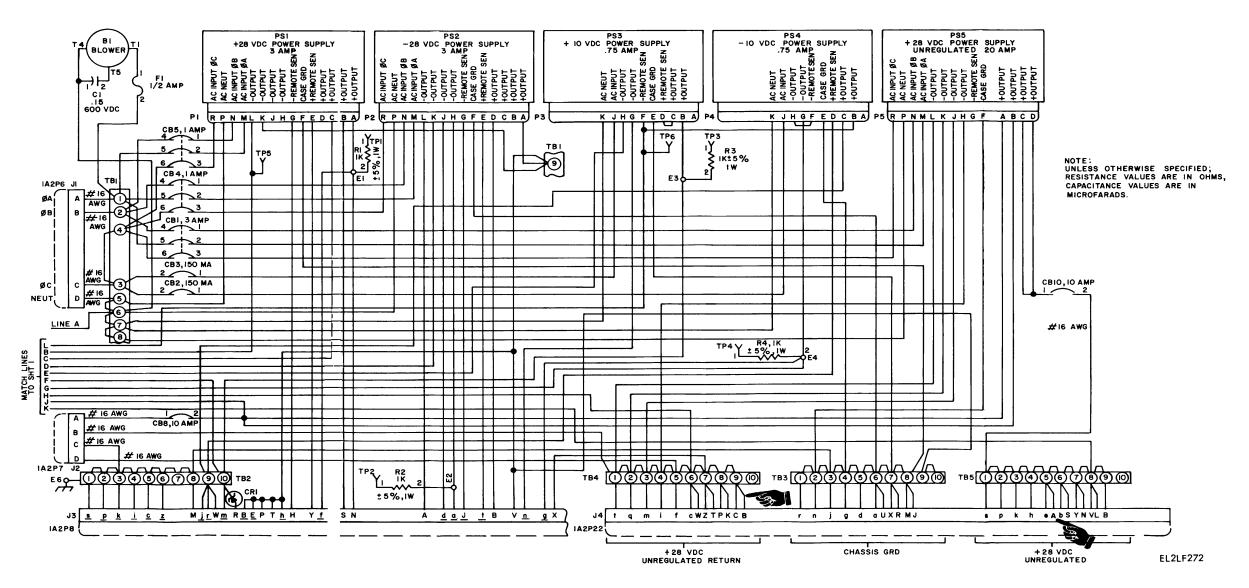

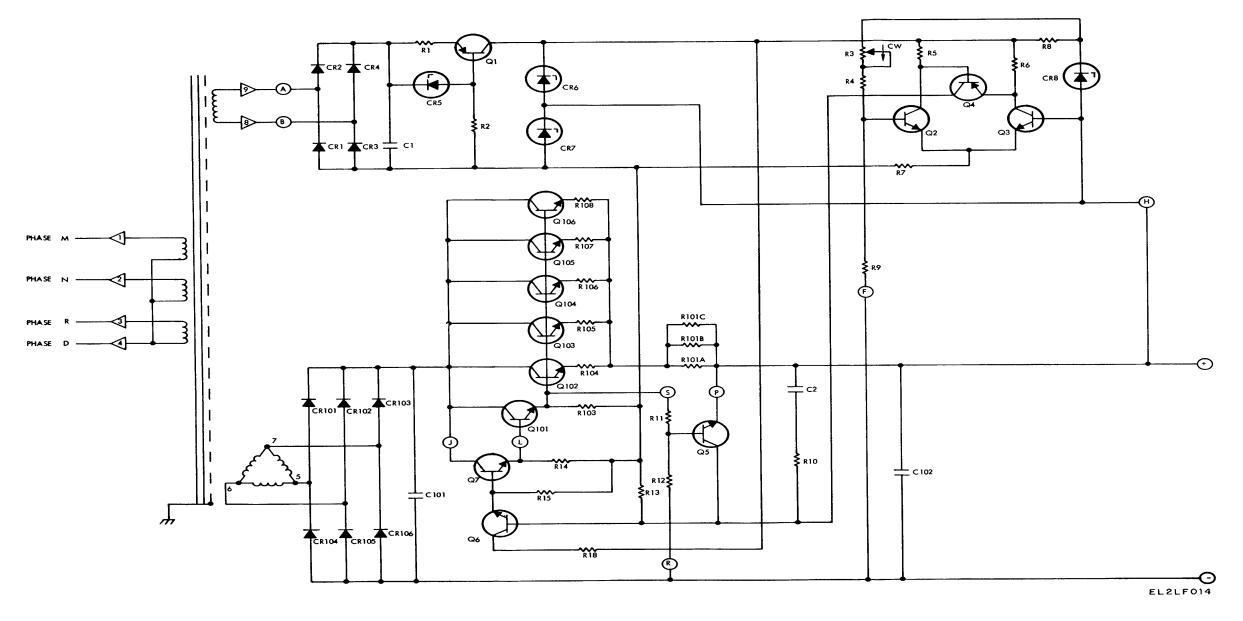

Power distribution panel 1A2AA contains five power supplies which provide positive and negative regulated voltages for the AN/TSC-54. All power supplies operate the same way, except component values are changed to develop a lower output voltage. Only the two +28 vdc power supplies are discussed.

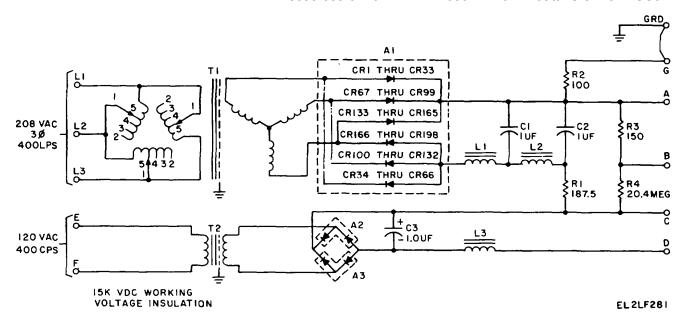

a. Positive 28 vdc power supply PS1 contains a 3-phase, 120/208 vac input transformer having a Y-connected primary and two secondary windings, two full-wave bridge rectifiers, and a regulation and sensing network. One secondary winding on transformer T101, a Y-connected stepdown winding, is connected to a full-wave bridge rectifier consisting of diodes CR101 through CR106. The full-wave bridge rectifier develops an output voltage across capacitor C101. Transistors Q101 and Q102 provide series regulation of the output voltage.

- The b. other secondary winding transformer T101 is connected to a full-wave bridge rectifier consisting of diodes CR1, CR2, CR3, and CR4. The full-wave bridge rectifier develops a voltage across capacitor C1, which provides bias for transistors Q1 through Q6. When the output voltage rises the potential on the base of transistor Q3 becomes more positive. Transistor Q3 conducts more heavily through resistor R7 driving the emitter of transistor Q2 more positive. Transistor Q2 conducts less through collector load resistor R5 and drives the base of transistor Q4 more positive. Transistor Q4 conducts less through resistor R13 decreasing the positive potential on the base of transistor Q6. Transistor Q6 conducts less through resistor R15 reducing the positive potential on the base of transistor Q7. Transistor Q7 conducts less through resistor R14 lowering the positive potential on the base of transistors Q101 and Q102. As transistors Q101 and Q102 conduct less, the voltage drop across them increases and returns the output voltage to the regulated value.

- When the output voltage decreases, the potential on the base of transistor Q3 becomes less Transistor Q3 now conducts less through resistor R7 driving the emitter of transistor Q2 less positive. Transistor Q2 conducts more heavily through collector load resistor R5 driving the base of transistor Q4 more negative. Transistor Q4 conducts more heavily through resistor R13 causing an increase in the positive potential on the base of transistor Q6. Transistor Q6 conducts more heavily through resistor R16 increasing the positive potential on the base of transistor Q7. Transistor Q7 conducts more heavily through resistor R14 increasing the positive potential on the base of series regulator transistors Q101 and Q102. transistors Q101 and Q102 conduct more heavily, the voltage drop across them decreases and returns the output voltage to the regulated value.

- d. Power distribution panel A4 contains 5 vdc

Zener diode CR1 which receives +10 vdc from power supply PS3 through TB2-10. Zener diode CR1 supplies +5 vdc through J3-R to J10-A of antenna control 1A2A5.

The +5 vdc is used by the scan generator logic circuits.

Figure 3-9. Typical +28 vdc/+10 vdc power supply, schematic diagram.

# 3-6. Plus 28 Vdc Regulated Power Supply PS5 Circuit Analysis

(fig. FO 3-3)

- a. The positive 28 vdc power supply PS5 contains a 3-phase, 120/208 vac input transformer having a Y-connected primary and two secondary windings, two full-wave bridge rectifiers and a regulation and sensing network. One secondary winding on input transformer T101, a delta-connected step-down winding, is connected to a full-wave bridge rectifier consisting of diodes CR101 through CR106. The full-wave bridge rectifier develops an output voltage across capacitor C101. Transistor Q102 through Q106 provide series regulation of the output voltage.

- b. The other secondary winding on transformer T101 is connected to a full-wave bridge rectifier consisting of diodes CR1, CR2, CR3 and CR4. The full-wave bridge rectifier develops a voltage across capacitor CI which is used to provide bias for transistors S1 through Q4.

- When the output voltage rises, the potential C. on the base of transistor Q3 becomes more positive. Transistor Q3 conducts more heavily through resistor R7 driving the emitter of transistor Q2 more positive. Transistor Q2 conducts less through collector load resistor R5 increasing the potential on the base of transistor Q4. Transistor Q4 conducts less through resistor R13 decreasing the positive potential on the base of transistor Q6. Transistor Q6 conducts less through resistor R15 decreasing the positive voltage on the base of transistor Q7. Transistor Q7 conducts less through resistor R14 decreasing the positive potential on the base of transistor Q101. Transistor Q101 conducts less through resistor R103 which decreases the positive potential on the base of transistors Q102 through Q106. As transistors Q102 through Q106 conduct less, the voltage drop across them increases and returns the output voltage to the regulated value.

- When the output voltage decreases, the potential on the base of transistor Q3 decreases. Transistor Q3 now conducts less through resistor R7 and this reduces the positive voltage on the emitter of Transistor Q2 conducts more heavily transistor Q2. through collector load resistor R5 driving the base of transistor Q4 more negative. Transistor Q4 conducts more heavily through resistor R13 increasing the positive potential on the base of transistor Q6. Transistor Q6 conducts more heavily through resistor R15 increasing the positive potential on the base of transistor Q7. Transistor Q7 conducts more heavily through resistor R14 increasing the positive potential on the base of transistor Q101. Transistor Q101 conducts more heavily through resistor R103 increasing the positive potentials on the base of transistors Q102 through

Q106. As transistors Q102 through Q106 conduct more heavily, the voltage drop across them decreases and returns the output to the regulated value.

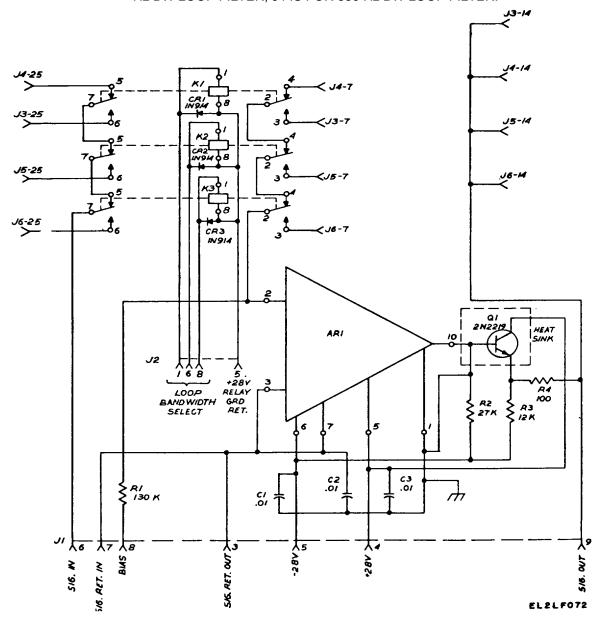

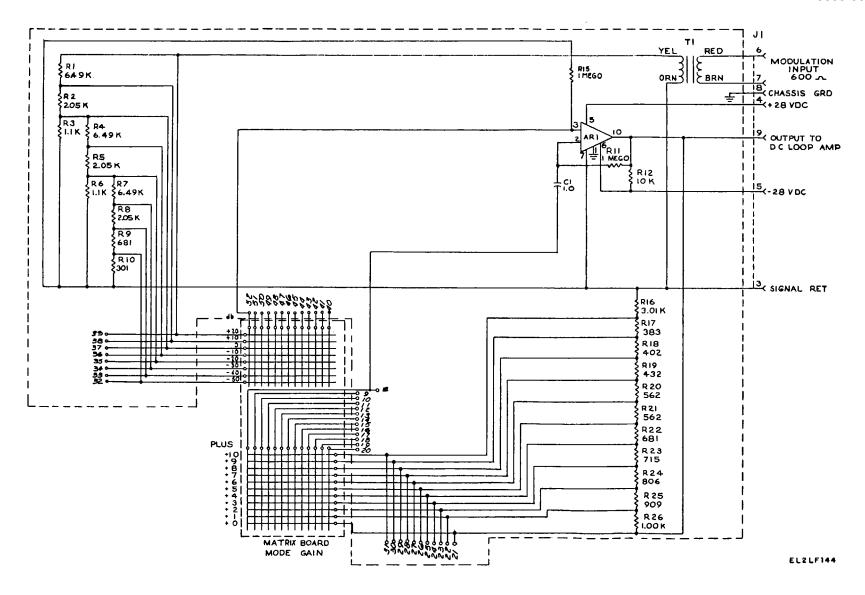

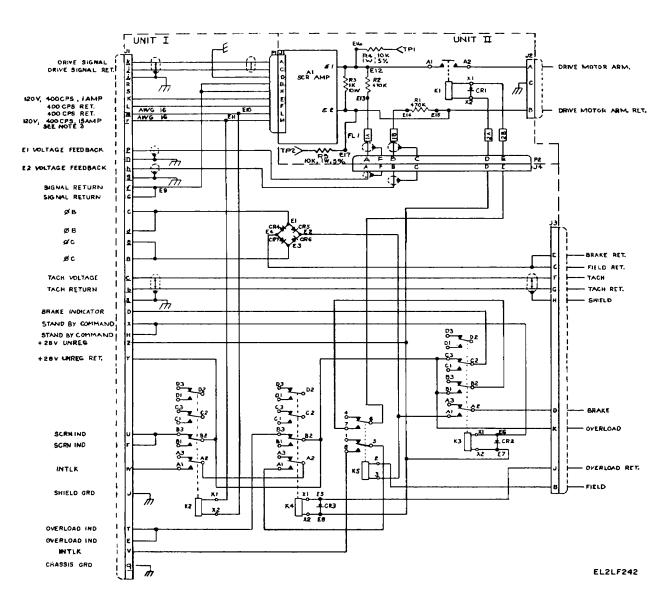

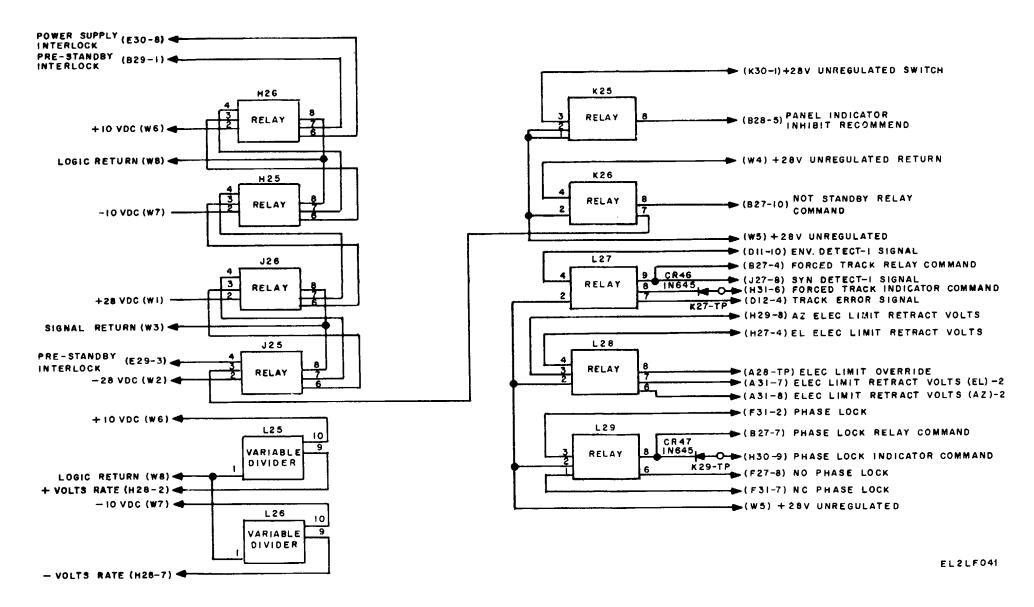

#### 3-7. Antenna Control Panel 1A2A5 Circuit Analysis

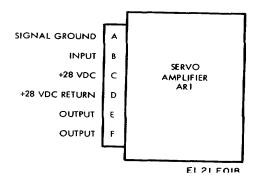

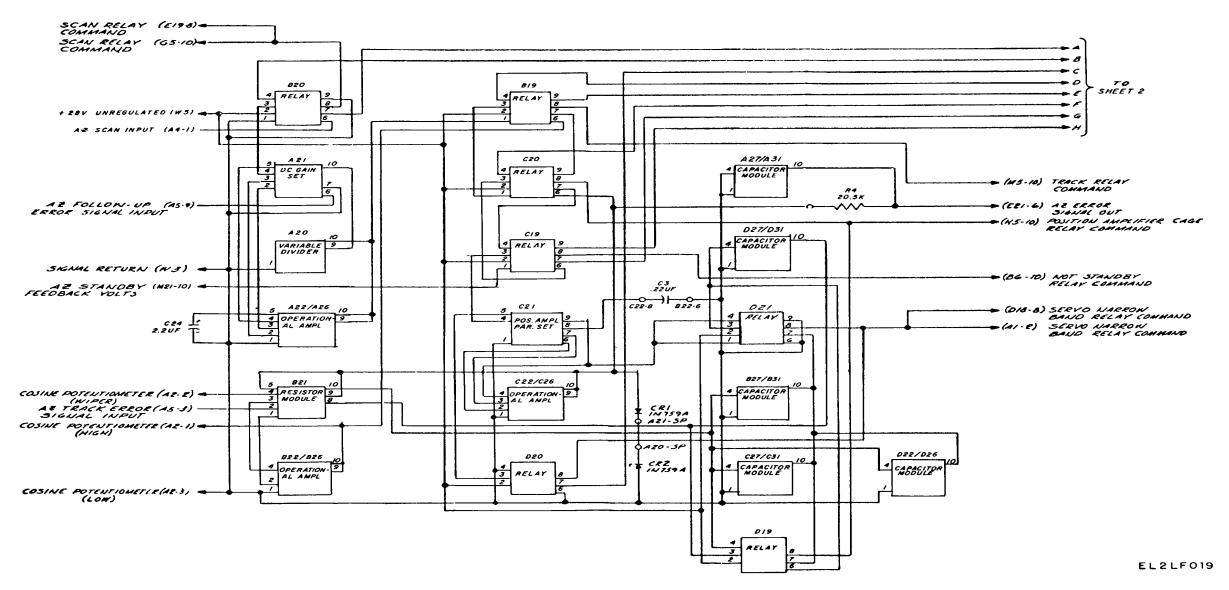

(fig. 3-10 through 3-14 and FO 3-4 through FO 3-8)

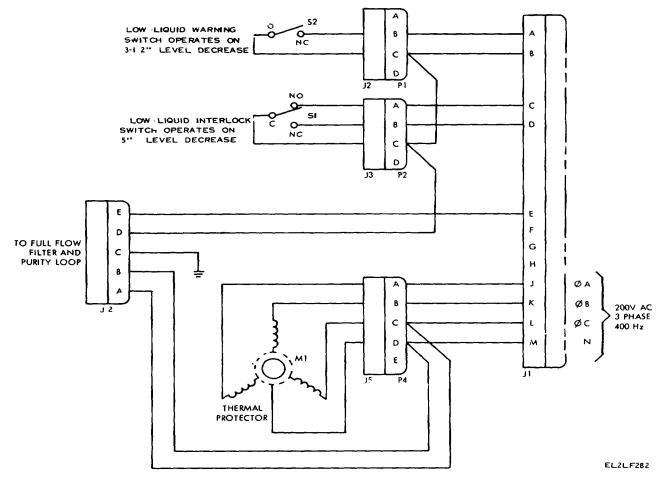

Antenna control panel 1A2A5 contains the circuitry (a through d below) used to control the positioning of the antenna.

- a. Scan generator A20 (fig. FO 3-5) produces signals for synchronizing the tracking error signal with the modulation taking place in the ferrite scanner.

- b. Upper module board A23 (fig. FO 3-7 and FO 3-8) is a hinged assembly mounted on the top of the chassis of the antenna control panel and contains electrical receptacles into which modules and cable connectors are plugged.

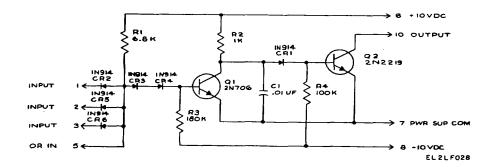

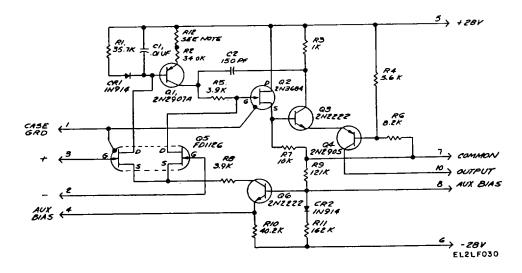

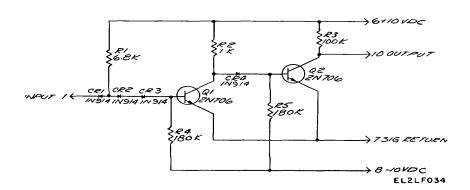

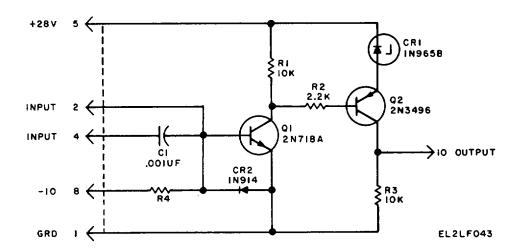

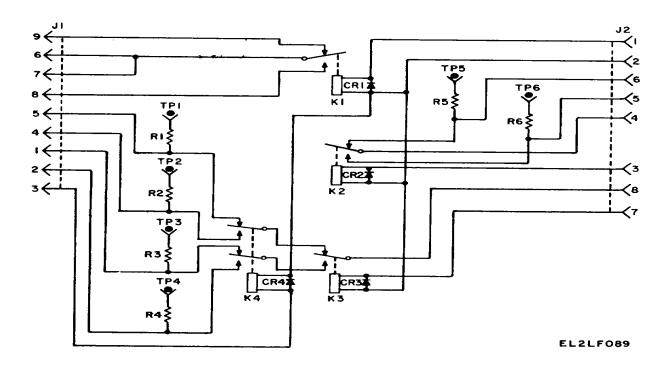

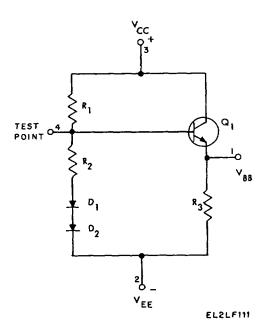

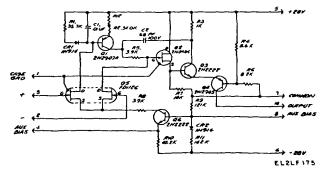

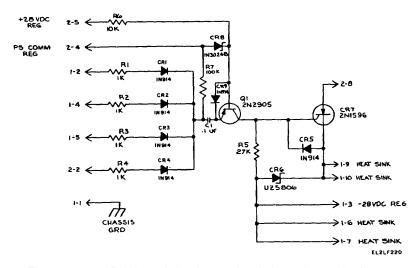

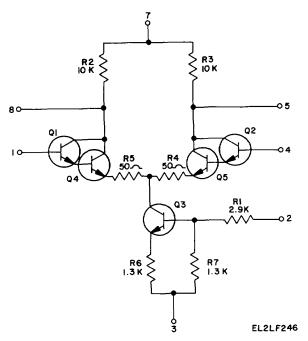

- (1) The relay driver (fig. 3-11) is used to provide a low driving impedance to energize relays. In the static state, with all of the diode coupled inputs connected to a minimum of +5.0 vdc or open, and the "OR" input is open, current flows from the +10 vdc voltage source through resistor R1, and diodes CR3 and CR4 to the base of transistor Q1; a small amount of current also flows through resistor R3 to the -10.0 vdc source. The current in the base of transistor Q1 causes it to conduct into a saturated state. The voltage at the collector of transistor Q1 will be approximately +0.4 vdc. A small amount of current will flow through diode CR1 and resistor R4 to the -10.0 vdc source and the voltage drop across diode CR1 will be approximately 0.5 vdc (this causes the cathode of diode CR1 to be a -0.1 vdc). The -0.1 vdc level on the base of transistor Q2, reverse biases the transistor and holds it in the off state.

- (2) If any of the inputs, including the "OR" input, are connected to ground, the current that was flowing into the base of transistor Q1 ((1) above) flows to ground through the grounded input and a small amount of current flows through diodes CR3 and CR4 and resistor R3 to the -10.0 vdc source (causing a voltage drop across diodes CR3 and CR4 of approximately 1.0 vdc). The anode of diode CR3 will be approximately +0.5 vdc or zero volt if the "OR" input is grounded, and the cathode of diode CR4 will be at -0.5 vdc or -1.0 vdc. The -0.5 or -1.0 vdc is also applied on the base of transistor Q1, which reverse biases the transistor holding it in the off state. The current that was flowing through transistor Q1 will now flow through diode CR1 into the base of transistor Q2 causing it to become saturated. Its collector will be at approximately +0.4 volts.

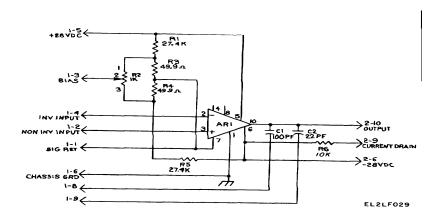

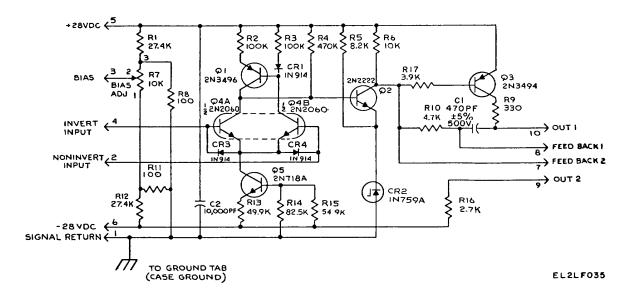

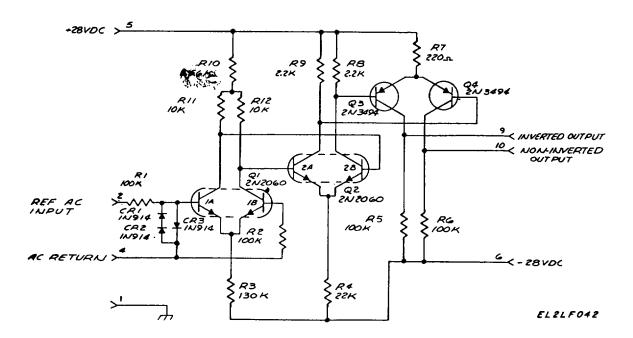

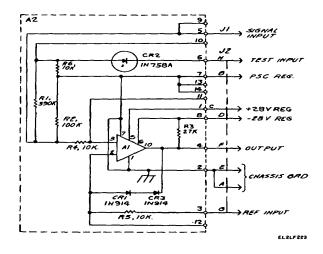

- c. Servo operational amplifier A3 (fig. 3-12) consists of a dc amplifier, a voltage divider, and feedback capacitors. The voltage divider contains a potentiometer which provides adjustment of the bias, to obtain a zero voltage offset on the output. The dc amplifier has the capability of providing an inverted or noninverted output. This is controlled by the application of the input signal to either pin 2 or 3.

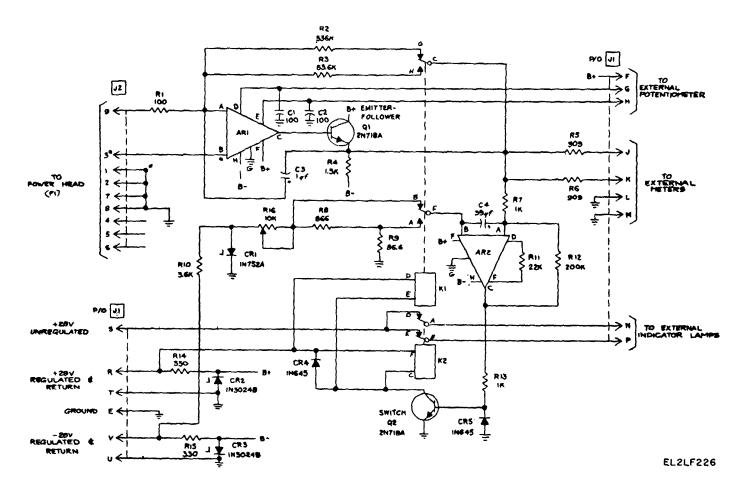

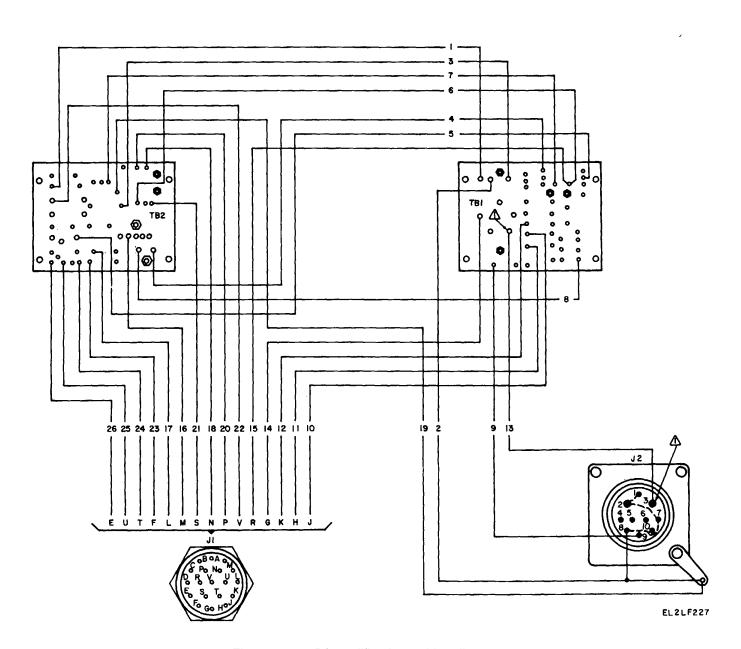

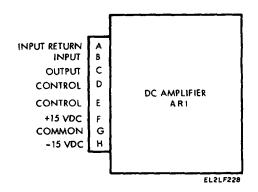

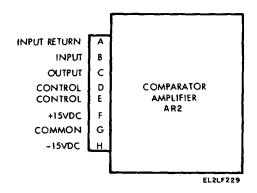

- (1) Dc amplifier AR1 (fig. 3-13) contains dual field effect transistor Q5 as the input stage, to provide isolation and drift stabilization. Transistor Q6 acts as a common constant current source for transistor Q5. Transistor Q1 is an inverter which drives field effect transistor Q2. The output from source follower Q2 is fed into emitter follower Q3 which drives the common base amplifier stage Q4. The collector of transistor Q4 is the output.

- (2) Dc bias and stabilization is obtained by feedback to the constant current source transistor Q6. Capacitors C1 and C2 provide frequency roll-off, so the circuit will not oscillate.

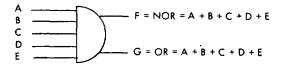

d. Gate expander A27 (fig. 3-14) consists of a 3-input diode gate, and a 2-input diode gate. These gates can be used in an AND or an OR configuration, and are also used to provide additional inputs .to transistor logic gates.

Figure 3-10. Servo amplifier AR1, input/output signal characteristics

Figure 3-11. Relay driver, schematic diagram.

Figure 3-12. Servo operational amplifier A3, schematic diagram.

Figure 3-13. Dc amplifier AR1, schematic diagram

Figure 3-14. Gate expander 1A2A5A23A27

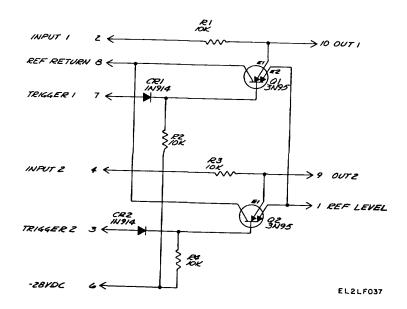

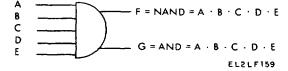

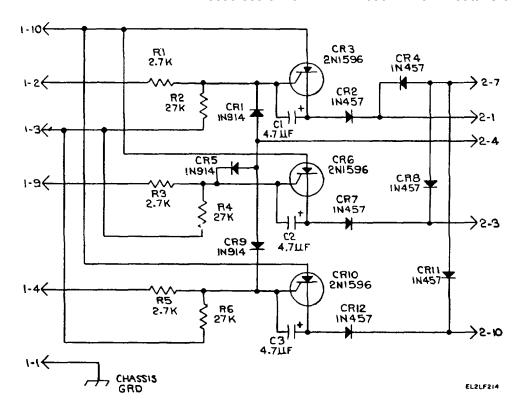

# 3-8. Dual NAND Gate A28 and NAND Gate A29 Circuit Analysis

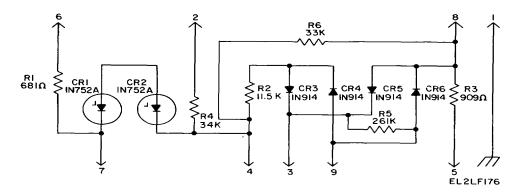

(fig. 3-15 and 3-16)

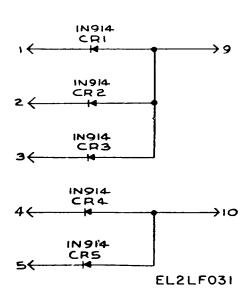

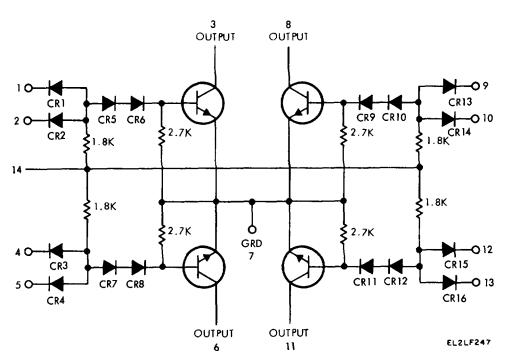

a. In the static state of the 3-input NAND gate, with all three of the inputs connected to a voltage level of +5 vdc or more, or open, current flows from the + 10 vdc voltage source at pin 6, through resistor R1 and diodes CR3 and CR4 to the base of transistor Q1. This current flow into the base of transistor Q1 causes Q1 to be in a saturated state, and its collector (pin 9) will be approximately -0.4 vdc above ground. A small amount of current also

flows through resistor R3 to the -10 vdc source. When any one of the three inputs is connected to ground, the current that was flowing into the base of transistor Q1 will flow through the diode that is grounded.

- b. A small amount of current will continue to flow through resistor R3 (a above), but the anode of diode CR3 is at a +0.5 vdc level, and the voltage drop across diodes CR3 and CR4 will be approximately 1.0 vdc. This causes the base of transistor Q1 to become back-biased and transistor Q1 will be in an off-state. When transistor Q1 is cut off, its collector (pin 9) will be at the +10 vdc level. The other NAND gate operates the same way, except that it has two inputs rather than three.

- c. The NAND gate performs exactly the same as the dual NAND gate described in a and b above, except it has five inputs and an OR input (fig. 3-16). The OR input causes the circuit to perform the same as the other inputs, except it is either open or grounded.

Figure 3-15. Dual NAND gate 1A2A5A23A28, schematic diagram.

Figure 3-16. NAND gate 1A2A5A23A29, schematic diagram.

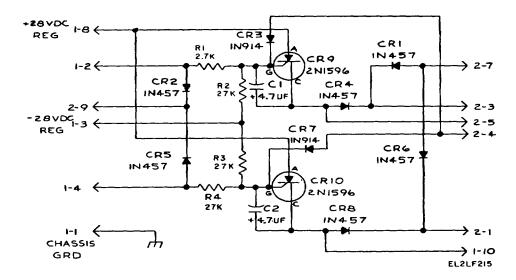

## 3-9. NAND Gate Driver A31 Circuit Analysis (fig. 3-17)

a. In the static state with the diode coupled input connected to a minimum of +5.0 vdc or open, current flows from the +10 vdc source through R1, CR2 and CR3 into the base of Q1; and a small amount of current flows through resistor R4 to the -10 vdc voltage source. The current flowing into the base of transistor Q1 causes it to be in a saturated state. The %Voltage at the collector of transistor Q1 will be approximately +0.4 vdc. A small amount of current will also flow through diode CR4 and resistor R5 to the -10 vdc source and the voltage drop across diode CR4 will be approximately 0.5 vdc. This causes the cathode of diode CR4 to be at -0.1 vdc. The -0.1 vdc level on the base of transistor Q2, reverse biases the transistor holding it in the off-state, and current will not flow.

If the input is connected to ground, the b. current that was flowing into the base of transistor Q1 (a above) flows to ground through diode CR1 and a small amount of current also flows through diodes CR2 and CR3, and resistor R4 to the -10 vdc source. This causes a voltage drop across diodes CR2 and CR3 of approximately 1.0 vdc. The anode of diode CR2 will be approximately +0.5 vdc and the cathode of diode CR3 will be at -0.5 vdc. The -0.5 vdc is also on the base of transistor Q1, which reverse biases the transistor holding it in the off-state, and current will not flow through it. The current that was flowing through transistor Q1 will now flow through diode CR4 into the base of transistor Q2 causing it to become saturated. Its collector will be at approximately +0.4 vdc.

Figure 3-17. NAND gate driver 1A2A5A23A31, schematic diagram.

# **3-10.** Operational Amplifier A61 Circuit Analysis (fig. 3-18)

a. The inputs to operational amplifier A61 are to differential connected stages consisting of transistors Q4A and Q4B. The emitters of transistors Q4A

and Q4B are connected to constant current source transistor Q5. The collector of transistor Q4B drives the base of transistor Q1, and the collector of transistor Q1 is connected to the collector of transistor Q4A. The two collectors are in phase with each other in order to achieve a very large voltage gain in this portion of the amplifier. The collectors

of transistors Q1 and Q4A drive into the base of transistor Q2.

b. The output from the emitter of transistor Q2 is applied to Zener diode CR2 and to the base of constant current source transistor Q5, through resistor R14. This produces an operating point feedback

and prevents the amplifier from drifting. The output from the collector of transistor Q2 is applied to the base of transistor Q3, which is the output stage of the amplifier. The collector of transistor Q3 is connected to the output through a 330-ohm current limiting resistor.

Figure 3-18. Operational amplifier 1A2A5A23A61, schematic diagram.

## 3-11. Level Shifter A63, Dual Low Level Switch A76 Circuit Analysis

(fig. 3-19)

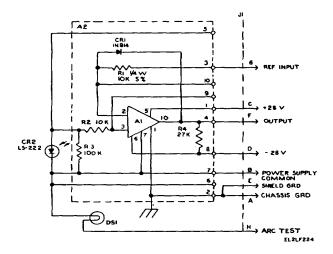

- a. When a high is present at the input of level shifter A63, diode CR2 is reverse-biased. Under this condition, current flows through the voltage divider consisting of resistors R4 and R1, and diodes CR3 and CR4. Transistor Q1 is forward-biased and current flows through collector load resistor R2. The decrease in voltage at the collector of transistor Q1 causes a decrease in voltage at the base of transistor Q2. Transistor Q2 is forward-biased, and is driven into saturation. The increased current flow through collector load resistor R5 causes the output voltage at pin 10 to be zero.

- b. When a low is present at the input of level shifter A63, diode CR2 is forward-biased. Current flows through diode CR2 and resistor R1. This places a reverse bias on the base of transistor Q1 and transistor Q1 is cut off. Since no current is flowing through collector load resistor R2, the rise in voltage at the collector of transistor Q1 is applied through resistor R3 to the base of transistor Q2. This places a reverse bias on transistor Q2, and it is driven into cutoff. With no current flowing through

collector load resistor R5, the output voltage at pin 10 drops to the negative potential at pin 6.

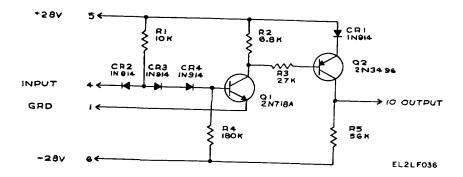

- c. Dual low level switch A76 (fig. 3-20) contains two tetrode transistor Q1 and A2. Although the transistors are connected to a common power source at pin 6, and a common reference level at pins 1 and 8, they operate identically as individual switches. For purposes of this manual, only transistor Q1 is discussed.

- (1) An input signal is applied to pin 2 and a trigger signal is applied to the anode of diode CR1. The trigger signal controls the gating action of the transistor. If the trigger signal represents a high, diode CR1 conducts and current flows through base bias resistor R2. Transistor Q1 is reverse-biased, and emitters E1I and E2 are virtually an open circuit. The input signal is coupled through resistor R1 to output pin 10.

- (2) When a low level signal is present at pin 7, diode CR1 is reverse-biased, and the base of transistor Q1 rises to the negative potential at pin & This places a forward bias on transistor Q1, and emitters E11 and E2 are effectively shorted together. Pin 10 is placed at the reference level, and the input signal at pin 2 is dissipated across resistor R1.

Figure 3-19. Level shifter 1A2A5A23A63, schematic diagram.

Figure 3-20. Dual low level switch 1A2A5A23A76, schematic diagram.

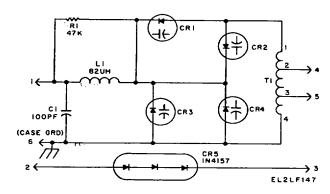

# 3-12. Lower Module Board 1A2A5A24 Circuit Analysis

(fig. 3-21 through 3-24 and FO 3-9)

Lower module board A24 is a hinged assembly mounted on the bottom of the chassis of antenna control panel 1A2A6 and contains electrical receptacles into which modules and cable connectors are plugged.

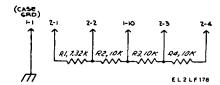

- a. Shaping circuit A24A1 (fig. 3-21) provides two square-wave outputs 180° out-of-phase with each other. The circuit contains two dual transistors, Q1 and Q2, and two signal transistors, Q3 and Q4. Their function is described in (1) through (4) below.

- (1) On the positive portion of the sinewave input, diode CR 3 conducts and limiting action occurs across resistor R1. Transistor QIA becomes forward-biased and causes an increase in current flow-through emitter resistor R3 and collector load

- resistor R11. The decrease in voltage at the collector of transistor Q1A is directly coupled to amplifier Q2B. The increase in current flow-through emitter resistor R3, reverse biases transistor Q1B and causes an increase in the collector voltage of Q1B. This increase in voltage is directly coupled to the base of amplifier Q2A.

- (2) Amplifier Q2A is now forward-biased and amplifier Q2B is reverse-biased. This results in an increase in voltage at the collector of amplifier Q2B and a decrease in voltage at the collector of amplifier Q2A. These outputs are directly coupled to the base of amplifiers Q3 and Q4. The increase in voltage at the base of amplifier Q3 causes an increase in reverse bias on amplifier Q3. The decrease in voltage at the base of amplifier Q4 causes an increase in forward bias on amplifier Q4. Under these conditions, current flow decreases through amplifier Q3, and increases through amplifier Q4.

The inverted output at pin 9 is taken across collector load resistor R6, and the noninverted output at pin 10 is taken across collector load resistor R6.

- (3) During the negative portion of the sinewave input, diodes CR1 and CR2 conduct, and limiting occurs across resistor R1. Transistor Q1A becomes reverse-biased and causes a decrease in current flow through emitter resistor R3 and collector load resistor R11. The increase in voltage at the collector of transistor Q1A is directly coupled to amplifier Q2B. The decrease in current flow-through emitter resistor R3 forward biases transistor Q1B and causes a decrease in the collector voltage of Q1B. This decrease in voltage is directly coupled to the base of amplifier A2A.

- (4) Amplifier Q2A is now reverse-biased and amplifier Q2B is forward biased. This results in an increase in voltage at the collector of amplifier Q2A and a decrease in voltage at the collector of amplifier Q2B. These outputs are directly coupled to the base of amplifiers Q3 and Q4. The decrease in voltage at the base of amplifier Q3 causes an increase in forward bias on Q3. The increase in voltage on the base of amplifier Q4 causes an increase in reverse bias on Q4. Under these conditions, current flow increases through amplifier Q3, and decreases through amplifier Q4. This action completes the cycle to convert the sinewave input to a square-wave output.

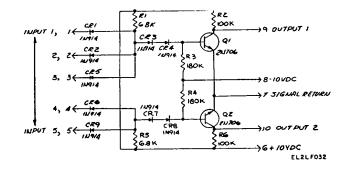

- b. Line driver A24A44 (fig. 3-22) is a twostage amplifier consisting of transistors Q1 and Q2 which, in the static state, are cutoff. The signal may be applied at either pin 2 or 4. Pin 4 provides a coupling capacitor C1 which blocks dc levels from the preceding circuit. Pin 2 is directly coupled to the base of amplifier Q1, and is normally used when the preceding circuit contains a coupling capacitor or is at a zero reference level.

- (1) Amplifier Q1 is biased at cutoff by a voltage divider network consisting of resistor R4 and diode CR2. A positive input signal forward biases transistor Q1 and allows current to flow through collector load resistor R1. This causes a decrease in voltage at the collector of transistor Q1, which is directly coupled to the base of transistor Q2 through resistor R2.

- (2) Transistor Q2 is a common emitter amplifier and its emitter is held at a constant reference level by breakdown diode CR1. The decrease in voltage on the base of amplifier Q2 increases the forward bias on the stage and allows it to conduct. Current flowing through collector load resistor R3 produces a positive signal in phase with the input signal.

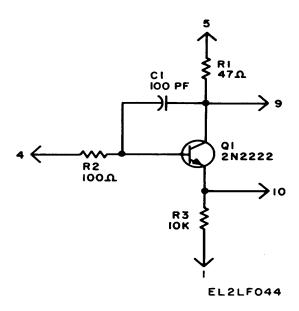

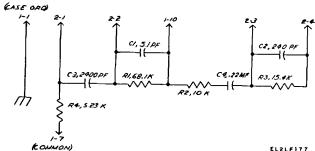

- c. Impedance amplifier A24A45 (fig. 3-23) is a single stage emitter follower. The output is taken across emitter resistor R3. Capacitor C1 provides degenerative feedback which improves the linearity and stabilization of the emitter follower.

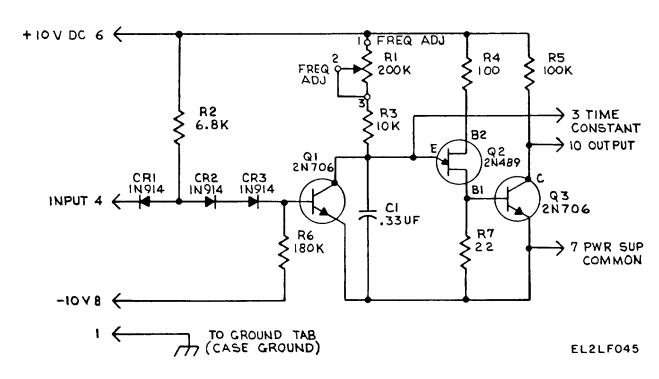

- d. Variable time delay A24A47 (fig. 3-24) consists of three transistor stages. During the static state, amplifier Q1 is forward-biased. Since amplifier Q1 is conducting, its collector voltage is low and there is no charge across capacitor C1. Therefore, the emitter voltage of unijunction transistor Q2 is low and it is cutoff. With no current flowing through unijunction transistor Q2 into the base of transistor Q3. Q3 will be cutoff.

- (1) When a negative pulse is present at the input (pin 4), diode CR1 is forward-biased, and the current that was flowing into the base of transistor Q1 now flows through diode CR1 to ground. Transistor Q1 is now reverse-biased and it cuts off. The collector voltage of amplifier Q1 attempts to rise but is limited by the charging current of capacitor C1. Capacitor C1 starts to charge through potentiometer R1 and resistor R3. The time constant is determined by the setting of potentiometer R1.

- (2) When capacitor C1 charges to a sufficient level to fire unijunction transistor Q2, current flows through base resistor R7 and a positive voltage is developed at the base of amplifier Q3. Transistor Q3 conducts through collector load resistor R5 causing the output voltage at pin 10 to decrease. The start of the output pulse was delayed from the start of the negative input pulse until capacitor C1 charged sufficiently to fire unijunction transistor Q2. At the end of the negative input signal, amplifier Q1 returns to the static state and starts to conduct. Capacitor C1 discharges through amplifier Q1 and unijunction transistor Q2 returns to cutoff, terminating the output pulse.

Figure 3-21. 70 MHZ shaping circuit 1A2A5A24A1, schematic diagram.

Figure 3-22. Line driver 1A2A5A24A44, schematic diagram.

Figure 3-23. Impedance amplifier 1A2A5A24A45, schematic diagram.

Figure 3-24. Variable time delay 1A2A5A24A47, schematic diagram.

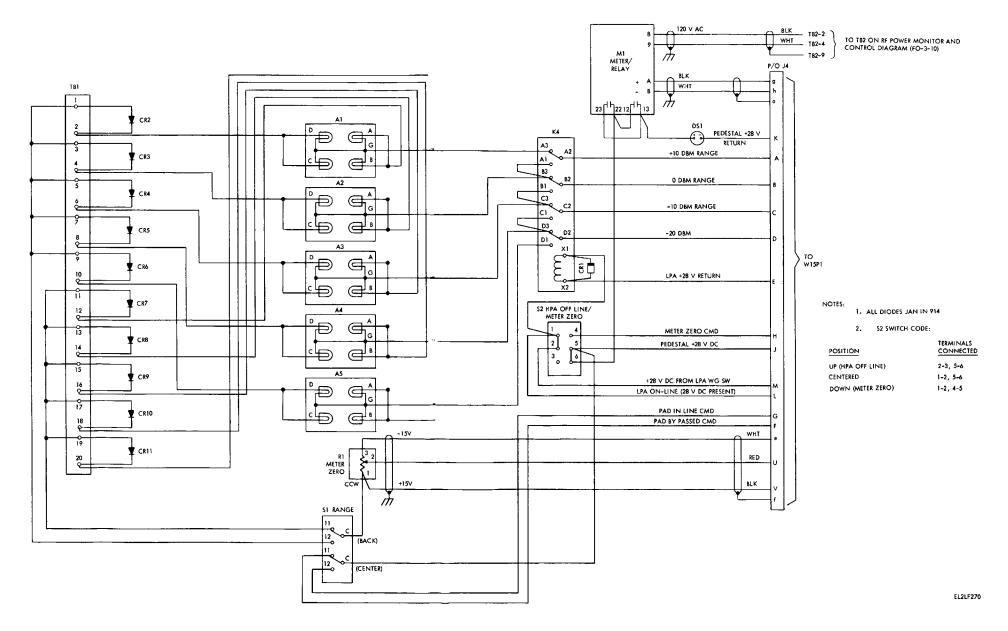

# 3-13. Rf Power Monitor and Control 1A2A27 Circuit Analysis

(figs. FO 3-10, FO 3-10.1 and FO 3-54)

a. The following subparagraphs describe the rf power monitor and control circuits of the common

power meter circuits, including on-line transmitter output power assembly 1A2A27A4.

b. Rf transmission line switch 2A3S2 (fig. FO 3-54) permits selection of either the LPA or HPA for monitoring by on-line transmitter output

power assembly 1A2A27A4. Switch 2A3S2 selects the attenuated rf output from HPA directional couplet 2A3DC6 (50 dB) or LPA directional coupler 2A3DC100 (40 dB). Each directional coupler rf output is routed through a variable attenuator (2A3A10AT18 for HPA, 2A3AT100 for LPA) to the rf transmission line switch The selected rf signal is then routed to rf transmission line switch 2A3A10S5. Control of switch 2A3S2 is by a +28 vdc input from the LPA routed to online transmitter output power assembly 1A2A27A4 (fig. 3-10.1). The command (which is present only when the LPA is on line) is routed through normally closed contacts of HPA OFF LINE-METER ZERO switch 1A2A27A4S2 to rf transmission line switch 2A3S2 (fig. FO 3-54). With LPA on line, the rf is routed from the No. 2 input to the IN port of switch 2A3S2 to switch 2A3A10S5.

- Switch 2A3A10S5 provides a meter zeroing attenuation for on-line transmitter output power. assembly 1A2A27A4 meter/relay M1 (fig. 3-10.1). When switch 1A2A27A4S2 is held in the METER ZERO position, +28 vdc (at 1A2A27A4J4-pin J, to 1A2A27A4S2 5-4 contacts) is sent to switch 2A3A 10S5 (fig. FO 3-54), disconnecting the selected rf monitoring sample from switch 2A3S2 and terminating the rf power head input with 2A3A10AT22. METER ZERO potentiometer 1A2A27A4R1 can then be used to zero the meter: R1 is connected to 40 dB autorange power meter amplifier 2A3A10A18 as an external zeroing drive. If switch 1A2A27A4S2 is not pressed, the rf from switch 2A3S2 is routed through the J143 connectors to rf transmission line switch 2A2A10S2. Switch 2A3S2 and switch 2A3A10S2 are rf transmission line switches. 2A3S2 contains a relay that connects the 1-IN ports together (when deenergized) or the IN-2 ports together (when energized). The METER ZERO position of switch 1A2A27A4S2 energizes the relay to connect the appropriate ports. Switch 2A3A10S2 has a double wound solenoid that connects the J142 and J3-J4 ports (switch position 1) or the J 14 and J2-3 ports (switch position 2). Each half of the solenoid is separately energized by 28 vdc which is applied by a switch; one solenoid input sets up position 1 and the other sets up position 2.

- d. Switch 2A3A10S2 (fig. FO 3-54) is controlled by RANGE switch S1 in on-line transmitter output power assembly 1A2A27A4 (fig. 3-10.1). RANGE switch S1 performs two functions: Control of rf switch 2A3A10S2 and dc power application to range indicators of the on-line transmitter. When RANGE switch S1 is set to the upper position, a pad bypass command is sent to rf transmission line switch 2A3A10S2, connecting the 1-4 ports and 2-3 ports. In this configuration the rf level from switch

- 2A3A 10S5 is routed through switch 2A3A10S2 to rf power head 2A3A10A22. If RANGE switch 1A2A27A4S1 is set to the lower position, ports 1-2 and 34 of rf switch 2A3A10S2 are connected together, putting attenuator 2A3A10OAT3 (5 dB) into the line ahead of the rf power head and isolator 2A3A10CP14.

- e. RF power head 2A3A10A22 (fig. 3-54) provides 40 dB autorange meter amplifier 2A3A10A18 with dc levels related to average power absorbed by the head. Refer to paragraph 3-13.1 for detailed analysis of amplifier 2A3A10A18.

- f. RF power monitor and control panel 1A2A27 (fig. FO 3-10) provides a means of continuously monitoring transmitter forward power output from 10 W to 10 kW (10ixW to 10 mW full scale). The rf power meter on this panel allows the operator to set the transmitter power, at any frequency, to within 0.2 dB over the power range of 10 W to 10 kW for the HPA, or 1 W to 3 kW for the LPA.

- On-line transmitter output power assembly 1A2A27A4 (fig. FO 3-10.1) allows the operator to set the high and low power automatic alarm points to within 0.5 db of the power meter reading. Alarm DS1 is triggered by the level setting through relay contacts of meter/relay assembly M1. The meter relay assembly is powered by 120 vac and controlled by the detected rf level at 40 dB autorange power meter amplifier A2A3A10A18. Threshold levels set by upper and lower level trip point adjustments on the meter face establish the point at which the relay of the meter/relay assembly will be energized. When energized (rf level being transmitted has exceeded or fallen below the preset level), the parallel-connected relay contacts close, and +28 vdc is connected through the 5-6 contacts of switch 1A2A27A4S2 (in its center position to the alarm). Four indicator ranges are provided to indicate the range level of the signal from 40 dB autorange meter amplifier 2A3A10A18. These ranges (+10, 0, -10, and -20 dBm) are displayed on indicator assemblies A1-A5 according to the status of relay K4 (energized when the LPA 2All is on-line; deenergized when HPA is on-line). indicator assembly contains two sets of lamps. Selection of the particular lamp set (top or bottom) is by RANGE switch S1 setting; high range (upper lamp set) or low range (lower lamp set). Power for the lamps (15 vdc) is provided from 40 dB autorange power meter amplifier through RANGE switch S1.

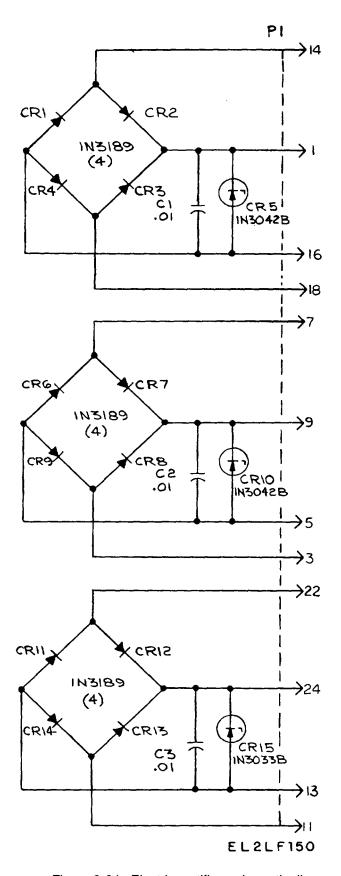

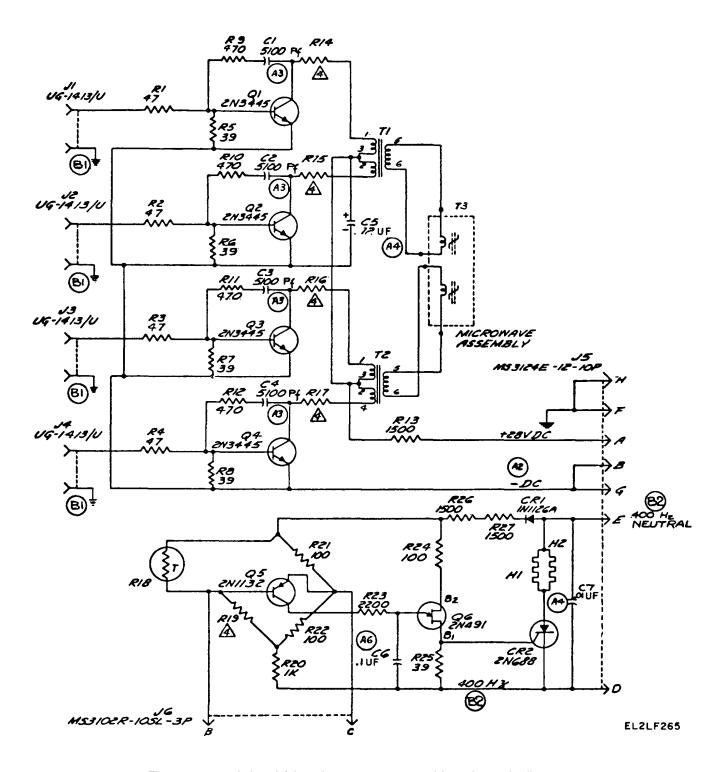

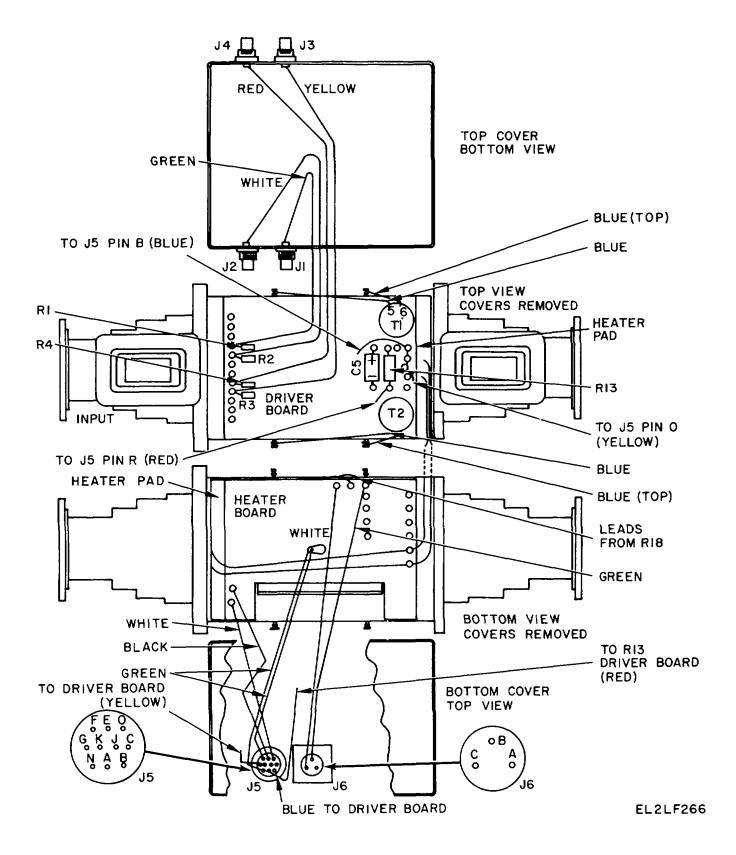

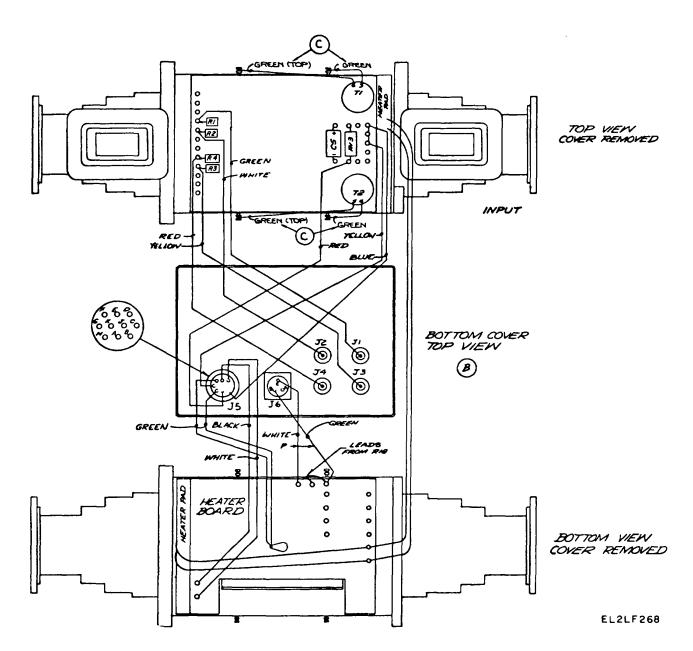

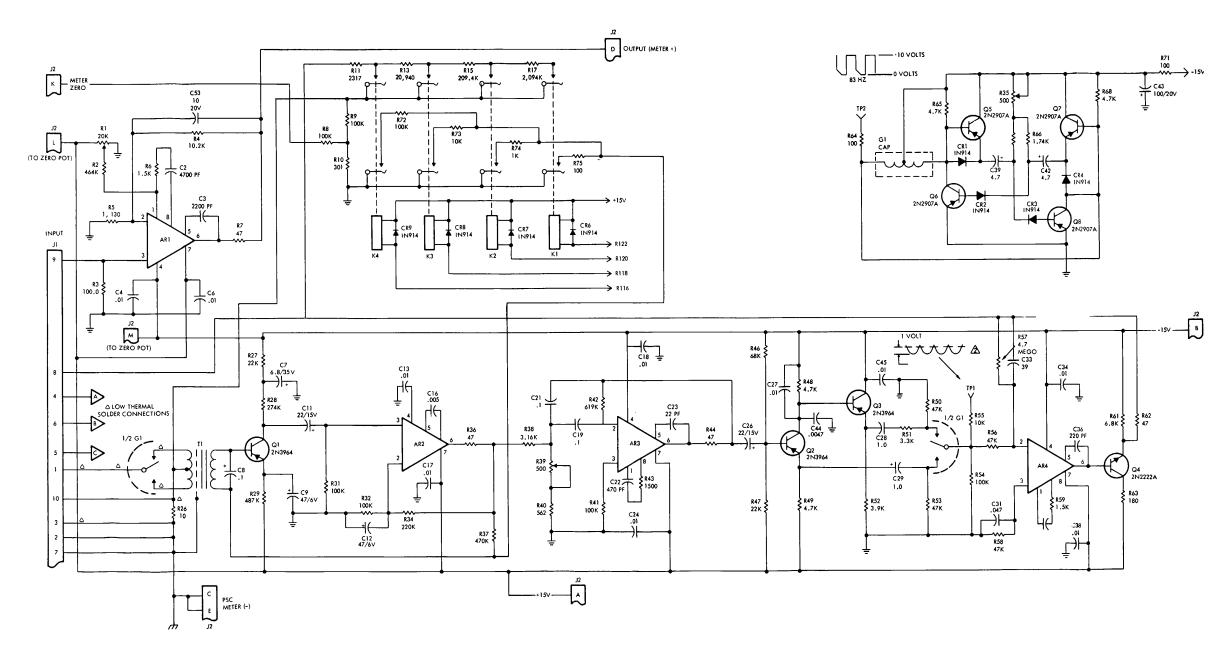

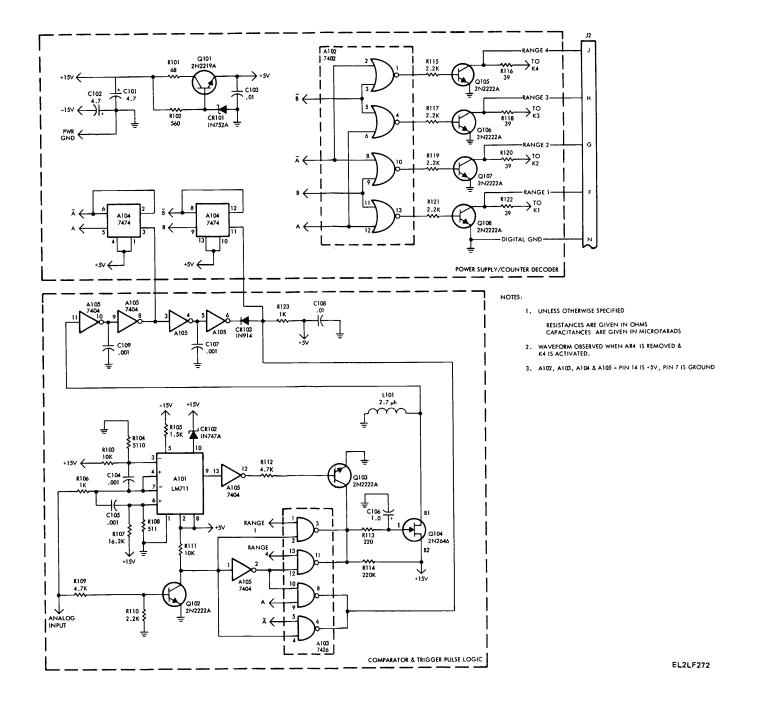

# 3-13.1. 40 dB Autorange Meter Amplifier 2A3A10A18 Circuit Analysis

(fig. FO 3-11)

a. The selected output from rf power head 2A3A10A22 is applied to 40 dB autoranging meter

amplifier 2A3A10A18. The dc input signal from the power head is applied to modulator G1-A (fig. 3-11). The square wave output signal of the modulator is stepped-up by input transformer T1 and applied to lownoise preamplifier Qi-AR2. The square wave signal is amplified in this circuit and coupled to filter amplifier AR3, where much of the noise and other spurious signals are filtered out. The resulting sine wave signal is then amplified and coupled to phase splitter Q2, Q3. This circuit provides the phase splitting action required to provide the demodulator input. The full wave demodulator (G1-B), which is synchronously driven with the modulator, recovers the input dc signal at a greatly amplified level.

- The output of the demodulator is applied to integrating amplifier AR4, Q4. This circuit provides additional signal gain, and also reduces the amplifier bandwidth to the degree required consistent with the selected response time (and noise level). The amplifier stage feedback capacitor determines the bandwidth of the dc amplifier and is controlled by the setting of RESPONSE switch S2. When in the NORM position, the response time of the power meter is less than 1 second and the noise is less than +1 percent p-p of full scale on the most sensitive range. When in the FAST position, the response time decreases to approximately 100 milliseconds, but the noise increases particularly on the low ranges. The output of the integrating amplifier is coupled back to the modulator and input transformer circuit through the switch network. This feedback provides a high degree of degeneration and, thus, gain stability, and at the same time provides a means of accurate control of the overall amplifier gain.

- c. The output of the integrating amplifier is also applied to the compensation network in the power head, where compensation is made for the sensitivity of the power head and for its inefficiency at the frequency of the signal under measurement. The return from the power head compensation network is applied to inverting amplifier AR1, and the output of this circuit drives meter M1 of on-line transmitter output assembly 1A2A27A4 through a second range switching network.

- d. Autoranging is accomplished by the components shown in the COMPARATOR AND TRIGGER PULSE LOGIC and POWER SUPPLY/COUNTER-DECODER areas of figure FO 3-11. Integrated circuit A101 and associated components comprise a double-ended limit detector network (comparator) which provides a nominal 3-volt output level (high) when the analog input signal is less than 0.45 volt or more than 5 volts, and a nominal 0-volt output level (low) when the analog input signal is between these two limits.

The lower limit value is determined by divider R107 and R108 and the positive power supply level, while the upper limit is determined by divider R103 and R104 and the positive power supply level. The comparator network output is inverted in A105 and applied to the base of common emitter amplifier Q103. If the comparator output is a low level, Q103 output is saturated at a dc level near zero, keeping capacitor C106 discharged and inhibiting range changes.

- e. The range switching rate network (Q104, R114, C 106) functions as a relaxation oscillator to provide trigger pulses to a two-stage binary up-down counter for the duration that comparator A101 is in the logic high state, if capacitor C106 is not clamped (c above). The time constant of this network is approximately 300 /sec, which allows up to three range changes each second, if necessary.

- f. Range switching is inhibited in one of the following three ways. First, when Q103 is in clamp (saturated) due to a low comparator output (which indicated an in-range condition); second, when the unit is in the most sensitive range and the analog input signal remains below 0.45 volt (power level less than 0.9 mW (g below); and third, when the unit is in the least sensitive range and the analog input signal remains above 5-volts (power level more than 10 mW).

- g. Counter A104 and associated components comprise the range switching network; stage A is referred to as A104A and stage B is referred to as A104B. Either binary stage will complement (flip) only when a positive-going pulse is applied to the appropriate clock input terminal. Switching occurs only between adjacent ranges, and can occur in either the forward or reverse direction. The following tabulation summarizes the four possible range combinations with 0 corresponding to low, 1 corresponding to high and A and B corresponding to the A104 outputs:

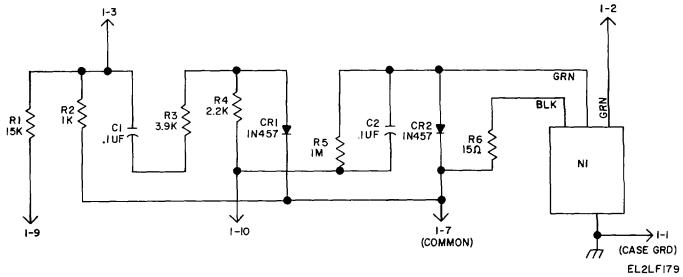

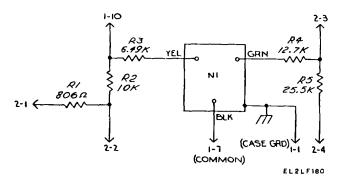

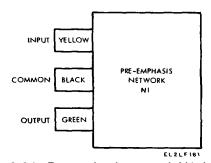

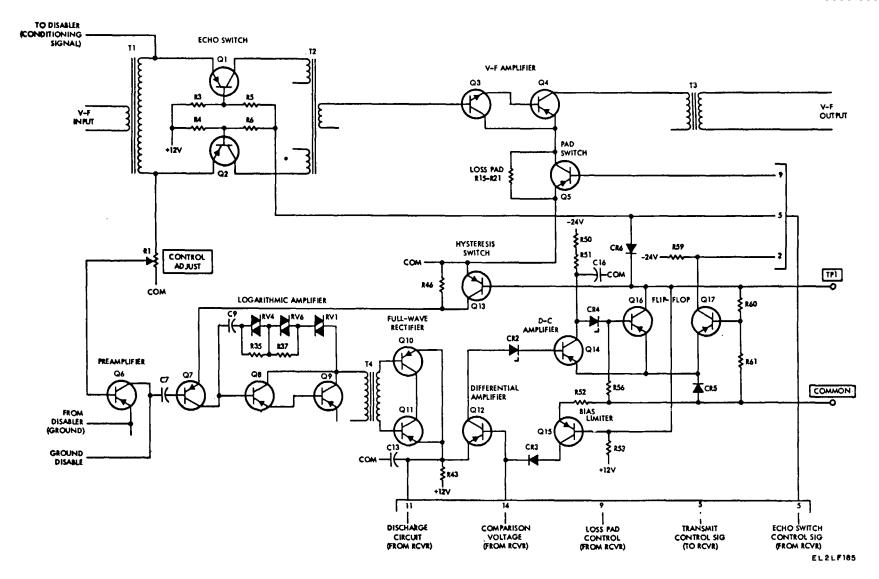

| A | В | Range | Full scale power input |